Computer Science & Information Technology 113

N. Ramasubramanian Rajeswari Sridhar M. Sridevi M. Brindha B. Shameedha Begum (Eds)

# **Computer Science & Information Technology**

First International Conference on Secure Reconfigurable Architectures & Intelligent Computing (SRAIC 2019) November 28 ~ 30, 2019, Tiruchirappalli, India

**AIRCC Publishing Corporation**

## **Volume Editors**

N. Ramasubramanian Professor, NIT, Trichy, India E-mail: nrs@nitt.edu

Rajeswari Sridhar Associate Professor, NIT, Trichy, India E-mail: srajeswari@nitt.edu

M. Sridevi Assistant Professor, NIT, Trichy, India E-mail: msridevi@nitt.edu

M. Brindha Assistant Professor, NIT, Trichy, India E-mail: brindham@nitt.edu

B. Shameedha Begum Assistant Professor, NIT, Trichy, India E-mail: shameedha@nitt.edu

ISSN: 2231 - 5403 ISBN: 978-1-925953-11-4 DOI: 10.5121/csit.2019.91501- 10.5121/csit.2019.91506

This work is subject to copyright. All rights are reserved, whether whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the International Copyright Law and permission for use must always be obtained from Academy & Industry Research Collaboration Center. Violations are liable to prosecution under the International Copyright Law.

Typesetting: Camera-ready by author, data conversion by NnN Net Solutions Private Ltd., Chennai, India

## Preface

The First International Conference on Secure Reconfigurable Architecture and Intelligent Computing (SRAIC 2019), November 29th to 30th 2019 with a pre-conference tutorial on November 29th 2019 is being scheduled at Department of Computer Science and Engineering, National Institute of Technology, Tiruchirappalli, INDIA in association with Department of Computer Science and Engineering, Dr. B.R Ambedkar Institute of Technology, sponsored by TEQIP – III and supported by IEEE Computer Society.

The conferences attracted many Indian delegates, presenting a balanced mixture of intellect from the East and from the West. The goal of this conference series is to bring together researchers and practitioners from academia and industry to focus on reconfigurable architectures and intelligent computing leading to new collaborations in these areas. This conference invited potential researchers to contribute to the conference by submitting articles that illustrate research results, projects, survey work and industrial experiences describing significant advances in all areas of reconfigurable architectures and intelligent computing. The conference committee rigorously invited submissions for many months from researchers, scientists, engineers, students and practitioners related to the relevant themes and tracks of the workshop. All the submissions underwent a strenuous peer review process which comprised expert reviewers. These reviewers were selected from a talented pool of Technical Committee members and external reviewers on the basis of their expertise. The papers were then reviewed based on their contributions, technical content, originality and clarity. The entire process, which includes the submission, review and acceptance processes, was done electronically. The extended papers of the conference will be reviewed for possible publication in "International Journal of Society Systems and Science" by Inderscience and "International Journal of Knowledge based organizations" by IGI – Global publishers.

We would like to thank TEQIP – III, IEEE Computer Society, our Director, Deans, the General and Program Chairs, organization staff, the members of the Technical Program Committees, the Tutorial and Keynote speakers, and external reviewers for their excellent and tireless work. We sincerely wish that all attendees benefited scientifically and able to bridge the gap in their research aspects. We the organizers wish that the conference brings together collaboration in the successive years to come by having joint proposals amongst the researchers and industry experts who have gathered here.

N. Ramasubramanian Rajeswari Sridhar M. Sridevi M. Brindha B. Shameedha Begum

## Patron's Message

Mini Shaji Thomas, Director, NIT, Trichy

"I believe in innovation and that the way you get innovation is you fund research and you learn the basic facts" says Bill Gates, CEO, Microsoft Corporation. We believed in this principle and used it to equip the Institution with the finest and latest infrastructure, state of the art libraries and laboratories, a formal and ideal learning environment with committed Faculty and supportive Administrative Staff.

I am happy to see that the Department of Computer Science and Engineering, National Institute of Technology, Trichy is organizing an International Conference for the first on the theme: "Secure Reconfigurable Architecture and Intelligent Computing" sponsored by TEQIP – III and supported by IEEE Computer society from 29th to 30th November 2019 with a pre-conference tutorial on November 28th 2019. I am also glad to learn that many academicians and research scholars especially from Asian continent are expected to participate in this conference.

International Conferences such as these provide an environment for academicians to interact, collaborate and share knowledge derived from their research in the field of Secure Reconfigurable Architecture and Intelligent Computing. I hope this conference would result in active coordination among researchers working in similar areas which would result in creative and innovative technologies leading to new research ideas for the benefit of society. The conference proceedings are published in AIRCC's "Computer Science and Information Technology" series. The extended papers of the conference will be reviewed for possible publication in "International Journal of Society Systems and Science" by Inderscience and "International Journal of Knowledge based organizations" by IGI – Global publishers.

As the Director, it gives me great pride to welcome the conference participants to enjoy their stay and make meaningful contributions that will, I am sure, widen the horizons of Intelligent computing.

(Mini Shaji Thomas)

## **Convener's Message**

N. Ramasubramanian Professor, NIT, Trichy.

"Understand well as I may, my comprehension can only be an infinitesimal fraction of all I want to understand" says English Mathematician and first computer programmer Ada Lovelace. These words made me believe that we need a common platform where researchers and students can share and exchange their ideas. We at the Department of Computer Science and Engineering, have just ventured into conducting International and National Conferences to share and impart knowledge to researchers and students.

In this direction, it gives me much pleasure to witness another major milestone for the department, to organize and conduct the First International Conference on Secure Reconfigurable Architecture and Intelligent Computing (SRAIC 2019), from 29th to 30th November 2019 with a pre-conference tutorial on November 28th 2019. The realization of success in organizing and hosting the conference goes a long way to not only showcase SRAIC as a major hub of CS research but also helps in transforming the Department of Computer Science and Engineering into a rich reservoir of research activity.

I wish, on behalf of SRAIC, to take this opportunity to thank all those who contributed in one way or other towards the success of the conference. My special thanks to the Tutorial Speakers and Keynote speakers who have participated in person and through video conferencing. I particularly appreciate the various paper presenters who have submitted well-researched and highly relevant presentations, and the SRAIC organizing committees for the long hours spent to ensure the success of the conference.

My heartfelt thanks to AIRCC for having agreed to publish the conference proceedings in their Computer Science and Information Technology Conference proceedings. My sincere thanks also goes to the conference sponsors, for the very generous assistance towards the organization of the conference. Continued consultations and cooperation of all parties mentioned above ensure that the first international conference in the Department of Computer Science and Engineering is indeed a remarkable success. Thank you once again and I encourage you to maintain this working spirit.

The conference program has been designed to provide ample opportunities for researchers to network and to share ideas and information about Secure Reconfigurable Architectures and Intelligent Computing. I hope this conference SRAIC 2019 will be enjoyable, memorable, and productive for participants and I look forward to the technological innovations that result from your networking and discussions.

### N. Ramasubramanian

## **Organizer's Message**

Rajeswari Sridhar Head, CSE Dept, NITT.

"Research is what I'm doing when I don't know what I'm doing" says Wernher von Braun, developer of the rocket technology of Nazi Germany. In addition, I reinstate research and innovation are necessary and essential components of a knowledgeable and growing society. Research ideas leading to innovative products to serve the society are primary inputs for achieving excellence in Education. The products that are off-springs of the research inputs, work as catalysts in the socio-economic progress of the Institution and in-turn the Country.

With this as a primary concept, National Institute of Technology, Trichy a leading Educational Institution in India, imparts quality education on par with international standards. The aim of National Institute of Technology, Trichy (NITT) is to create world class facilities to support Research and Innovation. To facilitate this support, with great pleasure and enthusiasm we formally announce and cordially invite you to the First International Conference on Secure Reconfigurable Architecture and Intelligent Computing (SRAIC 2019), to be held at National Institute of Technology, Trichy, India, from 29th to 30th November 2019 with a pre-conference tutorial on November 28th 2019.

The theme of the conference is Secure Reconfigurable Architecture and Intelligent Computing with the focus on thrust areas of Computer Science. This innovative educational forum will enable you to advance your knowledge and rewire the contemporaries which will open up new professional contacts amongst the National and International experts in this field. SRAIC 2019 is designed to be an academic feast, with a structured programme in a manner where participants will have ample time to interact after the sessions, which will be enriched by the presence of distinguished International and National Faculty.

With the right vision, right people and programs in the right place, we at the NITT make an attempt of creating the right set of contributions for different disciplines of research. The aim of education at National Institute of Technology, Trichy is to assist the students in developing their intellectual, aesthetic, emotional, moral and spiritual being. We, at NITT, impart futuristic, stress free education and instill high degree of discipline among them thereby setting global standards and making our students think logically and analytically.

I believe SRAIC would help achieve the above-mentioned aspects and I am sure would be a colossal success and bring tributes.

#### Rajeswari Sridhar

## **General Chair**

## Organization

| N. Ramasubramanian | National Institute of Technology- Trichy, India |

|--------------------|-------------------------------------------------|

| Rajeswari Sridhar  | National Institute of Technology- Trichy, India |

| M. Sridevi         | National Institute of Technology- Trichy, India |

| M. Brindha         | National Institute of Technology- Trichy, India |

| B. Shameedha Begum | National Institute of Technology- Trichy, India |

#### **Program Committee Members**

S. Selvakumar N. Ramasubramanian K. Viswanathan Iyer Leela Velusamy Mary Saira Bhanu C. Mala Rajeswari Sridhar Gandadharan G. R. Dominc M. Sridevi M. Brindha B. Shameedha Begum R. Mohan S. Jaya Nirmala E. Sivasankar Kunwar Singh B. Nithya Santhana Vijayan S. Sangeetha U. Srinivasulu Reddy Alagusundaram Harshabardhan S

Director, IIIT, Una Professor, NIT, Trichy NIT, Trichy NIT, Trichy Professor, NIT, Trichy Professor, NIT, Trichy Professor, NIT, Trichy Associate Professor, NIT, Trichy Associate Professor, NIT, Trichy Associate Professor, NIT, Trichy Assistant Professor, NIT, Trichy Professor, DBRAIT, Andaman Assistant Professor, DBRAIT, Andaman

## **Technical Committee**

K. Chandrasekaran Jaidhar C. D. G. Deepa P. C. Siddalingaswamy SRIRAM .G. SANJEEVI Rashmi Ranjan Rout N. Renugadevi Suresh Babu E Noor Mahammad SK Sivaselvan B Manoj Singh Gaur Meenakshi Tripathi Arka Prokash Mazumdar Ramesh Babu Battula Ayan Seal Pritee Khanna Mamata Dalui Chakraborty Saravanan Chandran Tanmay De Nanda Dulal Jana Sandip Karmakar Goutam Sanyal Anirban Sarkar Bibhash Sen Jayadeep Pati Sudip Roy Vijay Bhaskar Semwal Bibhudatta Sahoo Durga Prasad Mohapatra Darshan Vishwasrao Medhane TANMOY HAZRA Albert Sunny Chandra Shekar Laskhminarayanan Sahely Bhadra R.S.Yadav Krishn K. Mishra **Dushyant Kumar Singh** Rajitha B Naveen Kumar B. Surendiran Ansuman Mahapatra Damodar Reddy Edla Veena Thenkanidivoor Keshavamurthy B.N.

NIT Surathkal NIT Surathkal Manipal institute of technology Manipal institute of technology NIT Warangal NIT Warangal NIT Warangal NIT Warangal **IIITDM Kancheepuram IIITDM Kancheepuram MNIT** Jaipur **MNIT** Jaipur **MNIT** Jaipur **MNIT** Jaipur **IIITDM** Jabalpur **IIITDM** Jabalpur NIT Durgapur IIT Ranchi IIT Roorkee MANIT-Bhopal NIT Rourkela NIT Rourkela **IIIT** Pune **IIIT** Pune **IIT Palakkad** IIT Palakkad **IIT Palakkad** MNNIT Allahabad MNNIT Allahabad MNNIT Allahabad MNNIT Allahabad IIIT Vadodara NIT Puducherry NIT Puducherry NIT Goa NIT Goa NIT Goa

Rajendra Prasath Viswanath Pulabaigari KARTHICK S **K HIMABINDU** NAGESH BHATTU SRISTY SRILATHA CHEBROLU Kaushal Kumar Shukla Amrita Chaturvedi Anish Chand Balaji Raman Prerana Mukherjee Rajendra Prasath Viswanath Pulabaigari T. Veni Arun Raj Kumar P Vasudevan A. R Virender Ranga Maheshwari Prasad Sing, Mantosh Biswas Kishore kumar Senapati **RAJU BHUKYA** Narendran Rajagopalan Chittaranjan Hota Rekh Ram Janghel Sanjoy Pratihar B. Surendiran NEENA GOVEAS Krishna Pratap Singh B. Vijayakumar PARTHA PAUL Sudip Roy Annappa SUDIP KUMAR SAHANA Govind P. Gupta Mak Sharma Asif Ekba Manish Kumar K K Shukla Anurag Singh Mamata Dalui Chakraborty Pradeep Singh Meenakshi D'Souza Sanjay K. Sahay

Sanjay K. Sahay Keshavamurthy B.N. Kabita Thaoroijam Sathyanarayana Vollala **IIIT** Andhra Pradesh **IIIT Andhra Pradesh** NIT Andhra Pradesh NIT Andhra Pradesh NIT Andhra Pradesh NIT Andhra Pradesh IIT Varanasi IIT Varanasi **IIIT** Chittoor **IIIT** Chittoor **IIIT** Chittoor **IIIT** Chittoor **IIIT** Chittoor NIT Calicut NIT Calicut NIT Calicut NIT Kurukshetra NIT Patna NIT Kurukshetra Birla Institute of Technology NIT Warangal NIT Puducherry Birla Institute of Technology & Science, Pilani-Telangana NIT Raipur **IIIT Kalyani** NIT Puducherry Birla Institute of Technology & Science, Pilani-Goa **IIIT** Allahabad BITS Pilani, Dubai Campus. Birla Institute of Technology, Mesra IIT Roorkee NIT- Surathkal Birla Institute of Technology, Mesra **NIT Raipur** School of Computing and Digital Technology-Birmingham-United Kingdom IIT Patna IIIT, Jhalwa-Allahabad IIT Varanasi NIT-Delhi NIT-Durgapur NIT Raipur **IIIT-Bangalore** Birla Institute of Technology & Science, Pilani-Goa NIT-Goa **IIIT-Manipur** IIIT-Naya Raipur

# Advisory Committee

| Albert Sunny                    | IIT Palakkad |

|---------------------------------|--------------|

| Chandra Shekar Laskhminarayanan | IIT Palakkad |

| Sahely Bhadra                   | IIT Palakkad |

| Asif Ekbal                      | IIT Patna    |

| Jayadeep Pati                   | IIT Ranchi   |

| Sudip Roy                       | IIT Roorkee  |

| Sudip Roy                       | IIT Roorkee  |

| Kaushal Kumar Shukla            | IIT Varanasi |

| Amrita Chaturvedi               | IIT Varanasi |

| K K Shukla                      | IIT Varanasi |

**Technically Sponsored by**

**IEEE Computer Society**

**Technically Sponsored by**

**TEQIP-III**

CODETANTRA

**Organized By**

First International Conference on Secure Reconfigurable Architectures & Intelligent Computing (SRAIC 2019) NIT Trichy -National Institute of Technology

## **TABLE OF CONTENTS**

## First International Conference on Secure Reconfigurable Architectures & Intelligent Computing (SRAIC 2019)

| Analysis of Faults in an n-bit self checking register 01 -                                | 17 |

|-------------------------------------------------------------------------------------------|----|

| Shunbaga Pradeepa T and Uma Maheswari S                                                   |    |

| <b>A Smart Solar PV Monitoring System using IoT</b> 19 - <i>Kavitha V and Malathi V</i>   | 33 |

| A Low-Cost Methane Absorption Fueling System in Wireless Sensor<br>Networks using SBC-MS  | 45 |

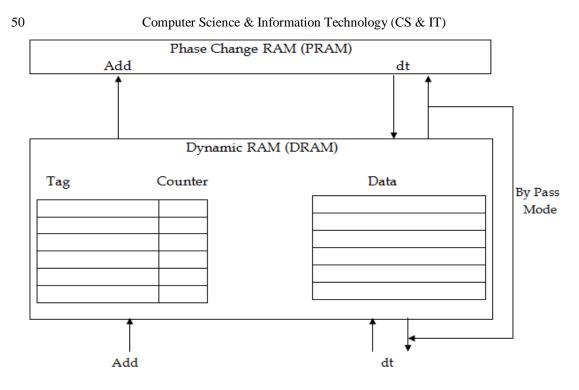

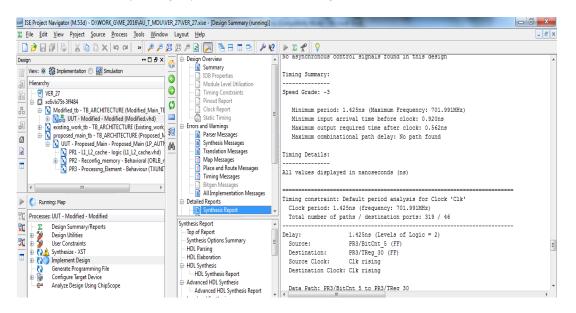

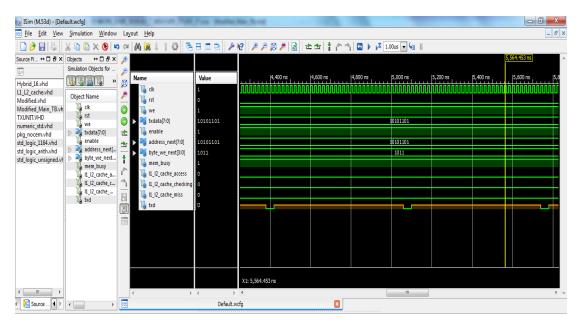

| <b>An Efficacious Runtime Adaptive Hybrid DRAM/PRAM Memory in</b><br><b>FPGA Platform</b> | 57 |

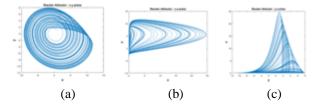

| Attractor Influenced PRNG for Cryptographic Key Generation on<br>FPGA                     | 70 |

| Machine Learning Model to Predict Birth Weight of New Born using<br>Tensor Flow           | 90 |

S.Karthiga, K.Indira, C.V.Nisha Angeline

# ANALYSIS OF FAULTS IN AN N-BIT SELF CHECKING REGISTER

T. Shunbaga Pradeepa<sup>1</sup> and S. Uma Maheswari<sup>2</sup>

<sup>1</sup>Assistant Professor, Department of Electronics and Communication Engineering, Coimbatore Institute of Technology, Coimbatore

<sup>2</sup>Professor, Department of Electronics and Communication Engineering, Coimbatore Institute of Technology, Coimbatore

#### **ABSTRACT**

Soft errors which are random errors induced by radiations may be produced due to transient faults and upsets in electronic systems. From the survey, it has been observed that the existing error correcting techniques and models have some limitations. The conventionally used error detection method named Triple Modular Redundancy (TMR) method has large overhead which makes it uneconomical. In this paper, the existing techniques like Time Redundancy based error Detection (TRDED) has been implemented and verified for different intervals of errors. It has been observed that only particular errors can be detected and no corrections are done. The modified circuits abbreviated as SETTOFF can be used for Soft Error and Timing Error Tolerant Flip Flop. These circuits which have both error correction and detection has been implemented and verified for different intervals of induced errors are increasing, there is a great necessity for developing a technique to provide more reliability and performance. Targeting towards the above features, self-checking register architecture for multi-bit error detection has been analyzed.

### Keywords

Transient Fault, Self-checking register, Single Event Upset (SEU), Multi bit error detection, Single Event Transient (SET)

## **1.** INTRODUCTION

Errors that occur randomly are Soft errors. They are induced by radiations that may be produced due to transient faults and upsets in electronic systems. Transient faults occur in 2 different ways. One is Single Event Upset that will change the state value in the storage cell. The other is Single Event Transients which generate transient voltage pulses in combinational gates. Memory elements are easily affected by SETs and sometimes they turn into soft errors. SEUs are a major concern in both dense memory arrays and sequential logic. The SEUs can be protected efficiently by conventional Error Correcting Code (ECC) techniques. But, since ECC is distributed across the entire system, they are not applicable in sequential logic. Therefore, there exists a challenge in achieving efficient error mitigation in general logic. The most widely used safety technique is Triple Modular Redundancy (TMR). This method eliminates errors in general logic. Although TMR is highly reliable, it requires large area which makes it uneconomical for most non-safety-critical electronics. Demands in Technology and customer are pushing performance and energy efficiency. However, the soft errors are becoming a major concern at the same time. To balance these conflicts, it is better to provide a convenient safety method in supporting non-safety-critical electronics. The First contribution of the work is the design and implementation of an error

N. Ramasubramanian et al.(Eds) : SRAIC-2019 pp. 01-17, 2019. © CS & IT-CSCP 2019

#### Computer Science & Information Technology (CS & IT)

tolerant D flip flop. In this method, to analyze cost-efficient error-tolerance in general logic a new design was done. The design is named Soft Error and Timing Error Tolerant Flip Flop. It is abbreviated as SETTOFF. This design can correct error upsets and detects transient errors. The errors that occur naturally are Timing Errors (TE).

The objective of this work evolves from the great interest in developing a technique to provide a better performing safety method that supports non-safety-critical electronics and in achieving more reliability and performance in detecting and correcting errors due to upsets and transients. Most sequential circuits do not have error correcting capability. So, they are easily induced to soft error especially in case of redundant circuits. If the combinational logic blocks with redundancies are unprotected, it will produce SET pulses which in turn may lead to occurrence of errors. If the redundancy is stable the particle striking can produce SEU as like in latch. So there exists a great need to achieve efficient error mitigation logic. The existing techniques use replication to improve the error tolerance level in any electronic system. But there exists some drawbacks. The techniques covers the errors are not protected. Those circuits are not checking themselves. It has become essential for Integrated Circuits to have some kind of circuits that detects soft errors as well as timing faults. Such protection is needed for all designs. One such tolerant design is TMR, but this seems to be costly.

Improvement in soft and timing error detection using time redundancy method have been implemented in Lorena Anghel and Michael Nicolaidis [4] based on time redundancy. Lin, M. Zwolinski, and B. Halak [15] have discussed a new architecture for Flip-Flop called SETTOFF which improves circuit performance to radiation hits against the existing ones. But, the cost area and performance are high. Yang Lin et al. has proposed [14] a technique to check circuits by itself for soft error based on SETTOFF. Sheng Lin et al. has proposed [11] circuits based on Schmitt trigger. The circuit uses conventional latch which increases the area consumed. Hsuan-Ming Chou et al. has presented [3] a design to protect from soft error targeting different applications with trade-off in performance, power, and reliability.

The flow of paper is like: Section 1 describing the overview and its related literature survey. Section 2 describes about the triple modular redundancy fault tolerant techniques. Basic idea about transient fault detection is given in Section 3. The study SETTOFF is briefed in Section 4. The architecture of proposed self-checking register is described in Section 5. Section 6 includes the implementation results of this work followed by conclusion in Section 7.

## 2. ARCHITECTURE OF TRIPLE MODULAR REDUNDANCY

Triple modular redundancy (TMR) is a method adopted in early days to obtain better safety system. The system has a majority voter. It reads data from three duplicate circuits. It then compares for majority of the outputs.

## 2.1. TMR Systems

2

TMR is a kind of fault tolerant system that is implemented in most computing system in the form of N modular redundancy. As the value of N is assumed as 3 meaning Tri, it is called Triple Modular Redundancy. This method has three systems performing the same process and the result of the process is taken by considering the majority value of the output. In this if one system is faulty, the other two systems will mask the fault in the system and it will correct the error automatically. The TMR is applicable to many redundant forms and also it is applicable in Error Correction Codes. TMR makes use of three identical and redundant form of the original system to compute its output. If there are no errors or faults in the systems all the redundant modules will produce the same output. If there are any errors then the outputs will be different.

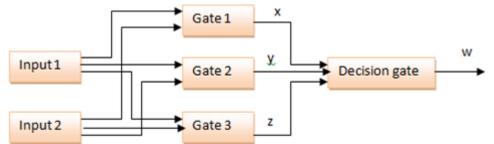

Figure 1. Triple Modular Redundant architecture

The circuit in Figure 1 represents the Triple Modular Redundant architecture where majority logic is used for finding the exact output in the circuit. If the circuits work properly without error, the outputs are same. The outputs will be different if the circuit has any failure. Majority gate is used in the circuit. It will help in finding the actual output. The logic output will be high value if more than two outputs are logic high. The logic output will be a low value if more than two inputs are logic low. The logic equation of the majority gate can be given as in Equation (1) where x, y and z are the inputs and w is the output of the majority gate.

$$w = (xy) \text{ or } (yz) \text{ or } (xz)$$

(1)

This has used AND logic as well as OR logic. Essentially the majority logic gate is a voting mechanism.

Consider the following scenarios that might occur in the majority gate. Let's say that logic 1 represents that there is no failure and logic 0 means the system has some failure.

Case (i) if there are no errors in the system, then all three modules will produce an output of 1, and the majority gate also produces a value of 1.

Case (ii) if any failure occurs in one of the modules then it produces an output of 0, but the other two modules are error free and produces an output of 1, the majority gate produces an output of 1. It is seen that even if one of the modules fail the error is masked by the other two modules.

Case (iii) if all the modules are producing an output of 0 then it will be reflected in the majority gate output. Conventionally, a fault-tolerant machine uses replicated elements which are operating parallel.

The TMR may be a robust form of error correction scheme but it doesn't indicate in which module the error has occurred. Also replication of the modules three times increases the hardware size required for fault free implementation. Although TMR is highly reliable, the large area consumption makes it uneconomical for most non-safety-critical electronics applications. There are other techniques to achieve cheaper solutions, but they are normally less reliable than TMR.

## 3. TIME REDUNDANCY BASED ERROR DETECTION

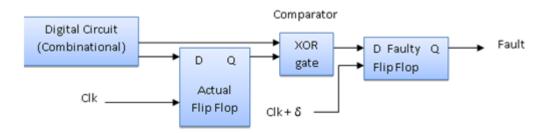

The Time Redundancy Based Detection abbreviated as TRD technique detects SET. It is found at the input of a flip flop by comparing the sampled data at two time instants delayed by delta. The error tolerance overhead of TRD is small as there is no duplication done. An SET pulse whose width is not greater than delta can be detected since it doesn't overlap the two time instances. The

#### 4 Computer Science & Information Technology (CS & IT)

TRD technique will detect timing errors that are caused due to previous logic modules, and the SEU occurring in the flip flop before the second time instance. Since the triplication is done the correct value is easily identified. The hardware redundancy achieves good tolerance in transient fault detection. The system is costly as because it is not suitable in commodity products. So, an alternate method of injecting transient faults is used.

## 3.1. Operating Principle

SET occurring in logic blocks can be corrected by themselves within a short period of time. They also recover automatically. There is no hardware duplication in the technique shown in Figure 2. TRD can detect SET for an the input of the flip flop whose pulse width can be maximum of Dtr <= delta - Dsetup - Dcomp,

where Dsetup is the time for setup of the error flip flop and Dcomp is comparator delay. The same SET if captured by the main flip flop at a time interval of t0, can be recovered at

t0 +  $\delta$  - Dsetup - Dcomp , whereas the comparator will produce an error output when the inputs are not consistent.

Figure 2. TRD Flip Flop

When the delay of TE is not greater than Dtr the fault can be detected and corrected for the input D. This architecture can also detect SEU in the main flip flop from t0 to  $t0 + \delta - Dsetup - Dcomp$ , which is called the TRD interval. TRD can detect but cannot correct errors. SEU in the main flip flop but outside the TRD interval cannot be detected by this module.

## 4. ERROR TOLERANT FLIP FLOP FOR SOFT AND TIMING ERROR

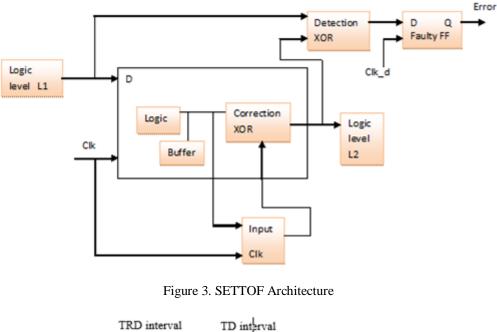

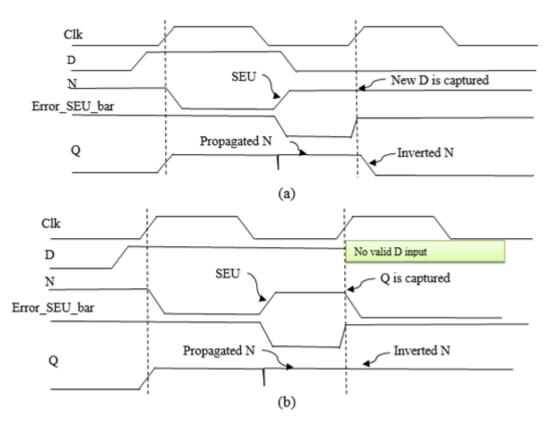

SETTOFF [15] overcomes the drawbacks of previous techniques and achieves a higher errortolerance with lower cost. The errors occurring during a write cycle of SETTOFF are detected and are easily corrected. Other errors which corrupt the data stored in SETTOFF are detected and corrected internally. If these errors are found to occur during a hold cycle, it is difficult to find it. The SETTOFF architecture is shown in Figure 3. The main flip flop is a normal flip flop. The last stage element has a pair of inverters. These inverters drive the output of the flip flop. They are now replaced by a correction XOR-gate. Therefore, in normal operation, the output variable Q is inverse of actual node N. The TRD interval of the clock phases high and low are as shown in Figure 4.

Module I is an adapted TRD architecture. It contains a XOR gate for detection and delayed clock is used to drive faulty Flip-Flop. The delay element  $\delta$  is the sum of Dhclk (period of the high clock phase), Ddxor (delay of XOR-gate detector) and Dsetup (faulty Flip-Flop set up time). The TRD interval is equal to  $\delta$  - Ddxor - Dsetup= Dhclk. During the write cycle of the main flip flop the error flip flop is enabled. Module I detect the type of error based on interval of TRD. It will be detected as SET if the L1 stage has a pulse width which is not greater than Dhclk. It detects as

timing error when a delay of module is not more than Dhclk and it detects as SEU if there is a change of state in node N during Dhclk. The error flip flop generates a signal when error is detected. Module I detects errors occurring during the write operation. Module II detects and corrects SEU occurring during the other half of the clock phase. Transition detector is present which monitors the internal node N. There is an XOR-gate which is used for correction purpose. Those SEU that corrupt the last stage of actual flip flop are considered, whereas others are masked. When TD is disabled the output (Error\_SEU\_bar) will remain high. This indicates errors are not present. The correction XOR-gate inverts N to Q.

Figure 4. SETTOFF's TRD and TD interval [13]

To further illustrate this, consider the three conditions shown in Figure.5.

Condition (i) Consider that SEU is correcting while writing in the flip flop, it will capture the input and checks if there have been any change in the bit value in the rising edge of the clock. Also, Error\_SEU\_bar is asserted and make the correction XOR-gate invert N to Q.

Condition (ii) the next case is when SEU is correcting when it is holding the data. Flip flop typically holds any of the two architectures either multiplexer based architecture or the clock gating based architecture. In a multiplexer based architecture, the input is in a hold cycle if the Flip-Flop captures an error, but the output Q is selected by a multiplexer to feed back into the input D. The Flip-Flop then captures the corrected Q to overwrite the SEU stored in the last inverter pair during the hold cycle. Error\_SEU\_bar is set to 1 at the same time.

#### Computer Science & Information Technology (CS & IT)

Condition (iii) in a clock-gating-based architecture, the driving clock in the flip flop is gated where there is no input capturing in hold cycle. The bit-Flip error remains at node N. This ensures that the flip of the bit remains corrected at Q. The process generates a correction glitch in the output of SETTOFF due to the delay in the propagation of the TD. The width of the fault is very small. This is due to the fact that the TD is relatively fast and the correction process is incorporated in the flip flop architecture. Even if the correction fault propagates, it is not fatal. SETTOFF has the ability of both error detection and correction. Some cases of errors have been detected and corrected using the modified D Flip Flop. SETTOFF can efficiently tolerate error upsets and timing errors.

Figure 5. SETTOFF Operating principle [13]

## 5. SELF- CHECKING ERROR TOLERANT REGISTER

Self-checking capability is not available in almost all pipeline protection techniques and hence they are easily affected by soft errors. The probability that the circuit is affected is determined by the area and size of the redundancies. But, the charge is used to determine the circuit's vulnerability. If the redundant modules are unprotected then ECC is needed at appropriate stages. The proposed technique takes has a self checking method implemented in register architecture.

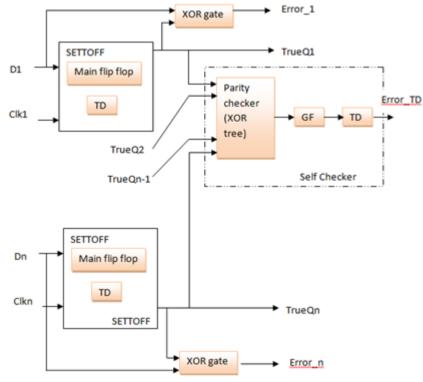

Then bit self checking register [14] is shown in Figure 6. It has n SETTOFF blocks which are shared with a self checker block. It also has a glitch filter (GF), and also includes a TD checker. The errors are combined together and are stored in the flip flop. As Module II is affected the error affects the output of a TD. The presence of self checker makes the process of monitoring the outputs. It then detects errors in Module II when there are any faulty transitions at these outputs.

The outputs of each bit are connected to the parity checker through n input XOR tree. The output is logic high when a fault is detected. This fault detection is made to pass through the Glitch

6

Filter. These transients may in turn induce glitches in the parity checker [16] output. The glitches are filtered and prevent them from passing. The errors that are detected can also be corrected.

Figure 6. n-bit self-checking register

### 5.1. Proposed Self-Checking Register for Multi-Bit Error Detection

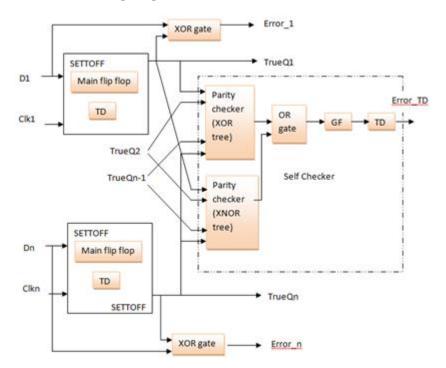

Figure 7. Proposed n-bit self-checking register with multi-bit error detection

#### 8 Computer Science & Information Technology (CS & IT)

The Figure 7 gives the n bit self-checking register architecture block. It has n SETTOFF and also has a self checking mechanism inbuilt as already in the Figure 6. This modified self checker can detect both odd and even number of soft errors. A self checker which is inbuilt monitors the outputs of all SETTOFF. The presence of parity checker helps in detecting odd number of errors using n input XOR tree. To detect even number of errors an n input XNOR tree is used. If errors are detected, the parity checker circuit generates a change in state. Thus, Self checking register gives more protection in pipeline architectures. The self checker has the capability of monitoring the outputs of each Flip Flops.

## 6. **RESULTS AND DISCUSSIONS**

The simulation results obtained in implementing various error tolerant techniques including time redundancy based error detection SETTOFF and the proposed self checking register for pipeline architectures are presented. Error tolerance analysis has been done using Xilinx ISE and Microwind Dsch tool was used for circuit analysis of SETTOFF.

## **6.1. Error Tolerance Analysis**

The discussed error resilient techniques were analyzed for different time intervals of forced errors.

## 6.1.1. Time Redundancy based Error Detection (TRD)

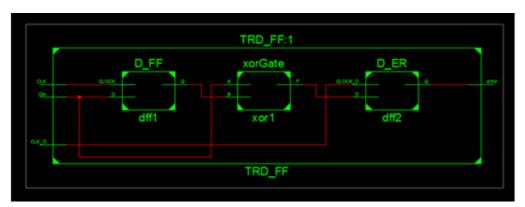

Figure 8 shows the RTL schematics of the TRD Flip Flop. It consists of an XOR gate with D Flip Flop. The XOR gate acts as the comparator. Comparator generates high value when an error is found.

Figure 8. RTL schematics of TRD

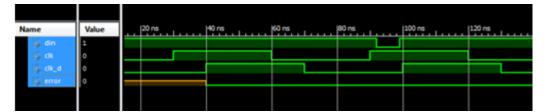

Figure 9. Error occurring from 92 ns to 105 ns

Figure 10. Error occurring from 92 ns to 99 ns

Figure 11. Error occurring from 88ns to 105 ns

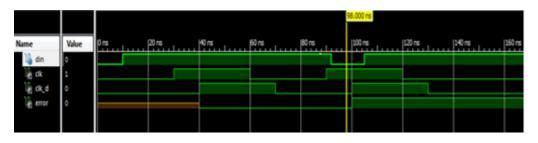

Figure 9 to Figure 12 shows the waveforms obtained for different intervals of errors that have been forced on the input Din. Clock period is taken as 60 ns and delay is given to the error flip flop as 10 ns. Since delay of clock transition occurs at 100 ns, the errors occurring as transitions before 90 ns and before 100 ns as well as after 90 ns and after 100 ns have been detected. But upsets which have transitions after 90 ns and before 100 ns are not getting detected. As well as, transitions occurring before 90 ns and after 100 ns are not getting detected.

| S.No | Error type                 | Inference                      |

|------|----------------------------|--------------------------------|

| 1    | Captured transients        | Output degraded, abided        |

| 2    | Error upsets (FF)and (TRD) | Output degraded but not abided |

Error tolerance analysis of TRD architecture is briefed and given in Table 1 and it shows that captured transients occurring external to the main Flip Flop will be corrupting the output and can be tolerated using the TRD architecture. But error upsets occurring in main Flip Flop and TRD architecture are not getting corrected even though they corrupt the output. So it can be inferred that TRD architecture doesn't have the capability to correct the error upsets occurring in the main Flip Flop.

#### 6.1.2. SETTOFF

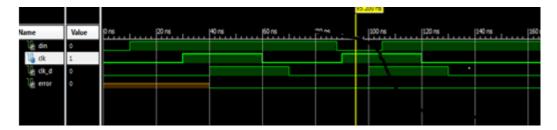

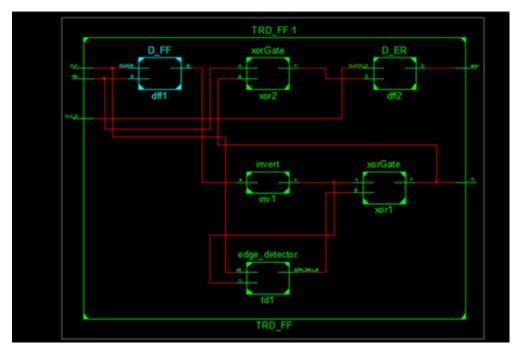

RTL schematic of SETTOFF is given in Figure 13. It consists of detection and correction modules for the conventional Flip Flop.

TRD part consists of the detection XOR gate and the error D Flip Flop. Correction part has correction XOR gate and the transition detector. The corrected output is taken from the correction XOR gate and error indication is taken from the TRD part.

The error detection waveforms given in Figure 14 to Figure 16 are same as in TRD architecture. Here clock period is taken as 60 ns and delay is 20 ns.

Figure 12. RTL schematic of SETTOFF

Figure 13. Error occurring from 88 ns to 99 ns

| Name              | Value | 0 ns | 50 ns | 100 ns | 150 ns | 200 ns | 250 ns |

|-------------------|-------|------|-------|--------|--------|--------|--------|

| ીસ din            | 1     |      |       |        |        |        |        |

| પશું હા⊀          | 0     |      |       |        |        |        |        |

| ીણું <b>તાર_ત</b> | 0     |      |       |        |        |        |        |

| le error          | 1     |      |       |        |        |        |        |

|                   |       |      |       |        |        |        |        |

|                   |       |      |       |        |        |        |        |

Figure 14. Error occurring from 92 ns to 112 ns

|           |   |       |     |       |        |       |       | 94 00 | 0.44   |        |     |

|-----------|---|-------|-----|-------|--------|-------|-------|-------|--------|--------|-----|

| Name      |   | Value | Pre | 20 mi | 140 ma | 60 ne | #0 ns |       | 300 ne | 120 ma | 1.0 |

| 14 din    |   | 0     |     |       |        |       |       |       |        |        |     |

| Line cite | . | 1     |     |       |        |       |       |       |        |        |     |

| 11 erro   |   | •     |     |       |        |       |       |       |        |        |     |

|           |   |       |     |       |        |       |       |       |        |        |     |

|           |   |       |     |       |        |       |       |       |        |        |     |

|           |   |       |     |       |        |       |       |       |        |        |     |

|           |   |       |     |       |        |       |       |       |        |        |     |

|           |   |       |     |       |        |       |       |       |        |        |     |

Figure 15. Error occurring from 92 ns to 99 ns

|                        |       |            |       |        | 93.080 | ) ns   |        |

|------------------------|-------|------------|-------|--------|--------|--------|--------|

| Name                   | Value | <br>140 ns | 60 ns | 180 ns |        | 100 ns | 120 ns |

| կել din                | 0     |            |       |        |        |        |        |

| 🗓 clk                  | 1     |            |       |        |        |        |        |

| ી <mark>શ</mark> clk_d | 0     |            |       |        |        |        |        |

| Ug error               | 0     |            |       |        |        |        |        |

|                        |       |            |       |        |        |        |        |

Figure 16. Error occurring from 88 ns to 112 ns

|                        |       | 1,070,460 ns                           |

|------------------------|-------|----------------------------------------|

| Name                   | Value | 1,000 ns 11,050 ns 11,100 ns 11,150 ns |

| Ling cik               | 0     |                                        |

| ՝ Լ <mark>ա</mark> din | 1     |                                        |

| 1 🚂 ո                  | 1     |                                        |

| L err_seu_b            | 0     |                                        |

| Ц_ Q                   | 1     |                                        |

| ી <mark>ક</mark> cik_d | 1     |                                        |

| COMPARATOR             | 0     |                                        |

| L error                | 0     |                                        |

|                        |       |                                        |

|                        |       |                                        |

Figure 17. Captured Q value

| Name                 | Value | <br>1,150 ns | 1,200 ns | 1,250 ns | 1, 800 ns | 1,350 ns 1,4 |

|----------------------|-------|--------------|----------|----------|-----------|--------------|

| l <mark>a</mark> din | 0     |              |          |          |           |              |

| l¦a dk               | 0     |              |          |          |           |              |

| Ug n                 | 1     |              |          |          |           |              |

| 🐚 error_seu_b        | 0     |              |          |          |           |              |

| ll q                 | 1     |              |          |          |           |              |

| l🔓 dk_d              | 1     |              |          |          |           |              |

| 1 error              | 0     |              |          |          |           |              |

|                      |       |              |          |          |           |              |

|                      |       | _            |          |          |           |              |

Figure 18. Propagation of n

|                         |       |               |          | 1,306.000 ns |           |          |

|-------------------------|-------|---------------|----------|--------------|-----------|----------|

| Name                    | Value | <br>1, 100 ns | 1,200 ns | ,300 ns      | 1,400 ns  | 1,500 ns |

| ີ ໄ <mark>ພີ</mark> din | 1     |               |          |              |           |          |

| ີ 🔓 dk                  | 0     |               |          |              | mains cor | rupted   |

| lig n                   | 1     |               | SEU      | - Ba         | mains cor | rected   |

| 🎼 error_seu_bar         | 0     |               |          |              | mains cor | rected   |

| પૈક્ષે વ                | 1     |               |          |              |           |          |

| ી <mark>હ</mark> ે dk_d | 1     |               |          |              |           |          |

| l 🔓 error               | 0     |               |          |              |           |          |

|                         |       |               |          |              |           |          |

Figure 19. Corrected Q

The delayed clock transition occurs at 110 ns. The errors having transitions before 90 ns and before 110 ns have been detected. But upsets which have transitions after 90 ns and before 110 ns are not getting detected. As well as, transitions occurring before 90 ns and after 110 ns are not getting detected.

For analyzing the correction process, errors have been injected at node 'n'. In all the above three cases which are given in Figure 18 to Figure 19, value of Q won't be interrupted. In Figure 17 Q value will be captured when upset is occurring at node 'n'. Figure 18 shows that the value at node

#### Computer Science & Information Technology (CS & IT)

'n' will be propagated to output Q when error occurs. When the value at node 'n' remains as corrupted, the value at output Q remains as corrected and this is given in Figure 19.

| S.No | Error type          | Inference                                     |

|------|---------------------|-----------------------------------------------|

| 1    | Captured transients | Output degraded, abided TRD                   |

| 2    | Error upsets (FF)   | Output degraded, abided TD based architecture |

| 3    | Errors (TRD)        | Output not degraded and abided                |

| 4    | Errors in (TD)      | Output degraded and not abided                |

Table 2. Error tolerance in SETTOFF

Table 2 gives the error tolerance analysis of SETTOFF. Particular intervals of errors can be detected and correction occurs for SEUs induced at the node 'n', which is the input of correction XOR gate. When compared to TRD architecture, SETTOFF has the capability of correcting the error upsets in the main Flip Flop.

#### 6.1.3. Self checking register

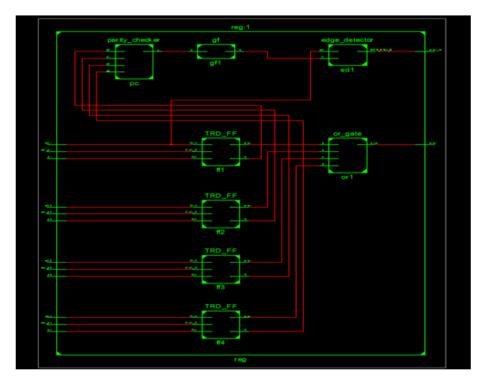

The self checker module has a parity checker for checking errors, a glitch filter for filtering and a transition detector as given in Figure 20. The error signals from each Flip Flop is given to an OR gate.

Figure 20. RTL schematic of self-checking register

| Name                | Value | 1,000 ns |

|---------------------|-------|----------|

| կ <mark>ո</mark> d1 | 1     |          |

| 11 d2               | 1     |          |

| 1🔓 d3               | 1     |          |

| l🔓 d4               | 1     |          |

| ါမြာ clk1           | 0     |          |

| ါြ clk_d1           | 1     |          |

| ြူ error            | 0     |          |

| 16 t1               | 0     | +        |

| 1 t2                | 1     |          |

| μ <sub>2</sub> t3   | 1     |          |

| ી <u>e</u> t4       | 1     |          |

| Ug el               | 0     |          |

| 1€ e2               | 0     |          |

| lie e3              | 0     |          |

| 1 <u>6</u> e4       | 0     |          |

| Ц <sub>е</sub> р    | 1     |          |

| ြြ error_td         | 0     |          |

|                     |       |          |

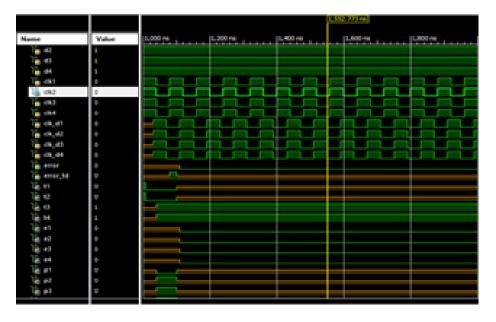

Figure 21. Output waveforms of self-checking register for single error detection

A single event transition is applied at the output of the first flip flop and the transition occurring at parity checker output is detected by the transition detector. As an indication of the error occurred at the first Flip Flop output, the output of the transition detector, error\_td signal, gets asserted.

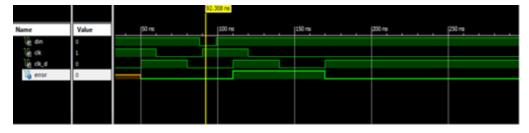

#### 6.1.4. Self-checking register for multi-bit error detection

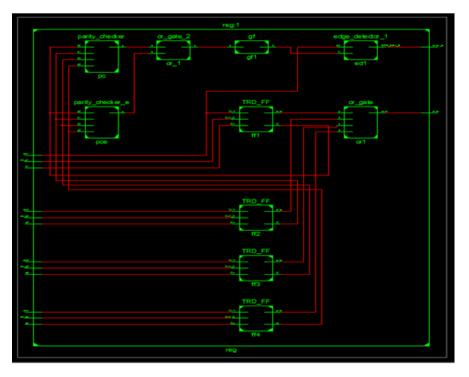

Figure 22. RTL schematic of self checking register for multi-bit error detection

The architecture in Figure 22 show self checking register for multi-bit error detection. An additional parity checker is given along with the self-checker to detect the multi-bit errors. The outputs from the parity checkers are given as the inputs to an OR gate and the output from this gate is then given to the glitch filter.

Figure 23. Output waveforms of self-checking register for single error detection

| Table 3 Analysis of error tolerance in | Self-checking register |

|----------------------------------------|------------------------|

|----------------------------------------|------------------------|

| S.No | Error type            | Inference                            |

|------|-----------------------|--------------------------------------|

| 1    | Captured transients   | Output degraded, abided TRD          |

| 2    | Error upsets (FF)     | Output degraded, abided TD           |

| 3    | Errors (TRD)          | Output not degraded and abided       |

| 4    | Errors (TD)           | Output degraded, abided Self-checker |

| 5    | Errors (self-checker) | Output not degraded and abided       |

Table.3. summarizes the analysis of error tolerance in self checking register. Self-checking register has more error tolerance capability. It detects the errors occurring in the TD-based architecture also compared to SETTOFF architecture.

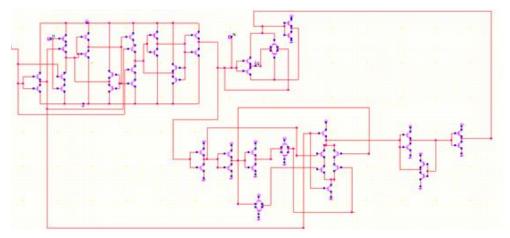

#### 6.2. Circuit Analysis

Figure 24 shows the circuit diagram of SETTOFF which has been implemented in Microwind Dsch tool. Fault analysis results are given in Figure 25 and Figure 26. Figure 25 shows the truth table of SETTOFF which is similar to that of conventional D Flip Flop. Test vector analysis of SETTOFF with stuck at faults at clock, input and internal nodes are given in Figure 26.

Figure 24. Circuit diagram of SETTOFF

| Truth-Table T | est Vectors |   |       |  |

|---------------|-------------|---|-------|--|

| clk           | D           | N | Q     |  |

| 0             | 0           | 0 | 65535 |  |

| 0             | 0           | 1 | 65535 |  |

| 0             | 1           | 0 | 65535 |  |

| 0             | 1           | 1 | 65535 |  |

| 1             | 0           | 0 | 0     |  |

| 1             | 0           | 1 | 0     |  |

| 1             | 1           | 0 | 1     |  |

| 1             | 1           | 1 | 1     |  |

Figure 25. Truth table of SETTOFF

| clk,D,N       | 000   | 001   | 010   | 011   | 100 | 101 | 110 | 111 |

|---------------|-------|-------|-------|-------|-----|-----|-----|-----|

| Q(fault-free) | 65535 | 65535 | 65535 | 65535 | 0   | 0   | 1   | 1   |

| clk@0         | ×     | x     | x     | ×     | ×   | ×   | ×   | ×   |

| clk@1         | 0     | 0     | 1     | 1     | 0   | 0   | 1   | 1   |

| D@0           | ×     | ×     | x     | ×     | 0   | 0   | <0> | <0> |

| D@1           | ×     | x     | х     | ×     | <1> | <1> | 1   | 1   |

| N@0           | ×     | х     | ×     | ×     | <1> | <1> | 1   | 1   |

| N@1           | ×     | ×     | ×     | ×     | 0   | 0   | <0> | <0> |

| Detect score  |       |       |       |       | 2/6 | 2/6 | 2/6 | 2/6 |

Figure 26. Test vector analysis of SETTOFF

Error tolerance analysis gives a comparison between the different techniques. The proposed one has more error tolerance capability.

## 7. CONCLUSION

A register with self checking capability has been proposed. The proposed system has been analyzed by introducing faults of different time intervals. It is found that the proposed system is error tolerant towards single event upset and timing errors. The system detects the error as well as corrects by itself with the help of in built self checking capability. The multiple errors are also detected and corrected. The fault analysis can be extended to other modules of digital sub blocks so that failures can be prevented. The system has a drawback of consuming more area. Techniques to reduce the area can be done in future.

#### REFERENCES

- [1] C. L. Chen, M. Y. Hsiao, (1984) "Error-correcting codes for semiconductor memory applications: A state-of-the-art review", IBM Journal of Research and Development. Vol.28, Issue.2, pp. 124 134.

- [2] C.H. Chen, D. Blaauw, D. Sylvester, Z. Zhang, (2014) "Design and evaluation of confidence-driven error-resilient systems", IEEE Transactions on Very Large Scale Integration (VLSI) systems, Vol.22, Issue.8, pp. 1727–1737.

- [3] Hsuan-Ming Chou, Ming-Yi Hsiao, Yi-Chiao Chen, Keng-Hao Yang, Jean Tsao, Chiao-Ling Lung, Shih-Chieh Chang, Wen-Ben Jone, and Tien-Fu Chen, (2015) "Soft-error-tolerant design methodology for balancing performance, power, and reliability", IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Vol.23, Issue.9, pp.1628–1639.

- [4] L. Anghel and M. Nicolaidis, (2000) "Cost reduction and evaluation of a temporary faults detecting technique," Proceedings Design, Automation and Test in Europe Conference and Exhibition 2000 (Cat. No. PR00537), Paris, France, pp.591-598.

- [5] M. Ebrahimi, A. Evans, M. B. Tahoori, R. Seyyedi, E. Costenaro and D. Alexandrescu, (2014) "Comprehensive analysis of alpha and neutron particle-induced soft errors in an embedded processor at nanoscales", Design, Automation and Test in Europe Conference and Exhibition (DATE), Dresden, pp.1-6.

- [6] M. Favalli and C. Metra, (2004) "TMR voting in the presence of crosstalk faults at the voter inputs", IEEE Transactions on Reliability, Vol. 53, No. 3, pp. 342-348.

- [7] M. Nicolaidis, (1999) "Time redundancy based soft-error tolerance to rescue nanometer technologies", Proceedings 17th IEEE VLSI Test Symposium (Cat. No.PR00146), Dana Point, CA, USA, pp. 86-94.

- [8] M. Zwolinski, (2001) "A technique for transparent fault injection and simulation in VHDL", Microelectronics Reliability, Elsevier Ltd., 41 (6), pp.797-804.

- [9] N.D.P. Avirneni and A. Somani, (2012) "Low Overhead Soft Error Mitigation Techniques for High-Performance and Aggressive Designs", IEEE Transactions on Computers, vol. 61, no. 4, pp.488-501, April 2012

- [10] N. Gaitanis, (1988) "The design of totally self-checking TMR fault-tolerant systems", IEEE Transactions on Computers, Vol. 37, No. 11, pp. 1450-1454.

- [11] S. Lin, Y. Kim and F. Lombardi, (2011) "Design and Performance Evaluation of Radiation Hardened Latches for Nanoscale CMOS", in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol.19, No. 7, pp. 1315-1319.

- [12] S. Mitra, N. Seifert, M. Zhang, Q. Shi and K. S. Kim, (2005) "Robust system design with built-in soft-error resilience", Computer, Vol.38, No.2, pp. 43-52.

#### 16

- [13] T. Calin, M. Nicolaidis and R. Velazco, (1996) "Upset hardened memory design for submicron CMOS technology", IEEE Transactions on Nuclear Science, Vol. 43, No. 6, pp. 2874-2878.

- [14] Y. Lin and M. Zwolinski, (2014) "A cost efficient self checking register architecture for radiation hardened designs", IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, pp. 149-152.

- [15] Y. Lin, M. Zwolinski and B. Halak, (2014) "A low-cost radiation hardened Flip-Flop", 2014 Design, Automation and Test in Europe Conference and Exhibition (DATE), Dresden, pp. 1-6.

- [16] Y. Lin, M. Zwolinski and B. Halak, (2016) "A Low-Cost, Radiation-Hardened Method for Pipeline Protection in Microprocessors", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 24, No. 5, pp. 1688-1701.

#### AUTHORS

**T. Shunbaga Pradeepa** is obtained her B.E. Degree in Electronics and Communication Engineering and M.E. Degree in VLSI Design. She has 4 years of industry (R&D) experience, currently she is working as Assistant Professor in the Department of Electronics and Communication Engineering at Coimbatore Institute of Technology, Coimbatore. She has around 10 years of teaching experience. She is currently doing research in the automotive safety architecture design. Her research interests are in the design and testing of analog and digital systems, Embedded Systems, VLSI design.

**Dr.Uma Maheswari** obtained her B.E. Degree in Electronics and Communication Engineering from Government College of Technology, Coimbatore, M.E. Degree in Applied Electronics from Coimbatore Institute of Technology and Doctoral degree in Electrical and Electronics Engineering with specialization in Biometrics, from Bharathiar University, Coimbatore. She is presently working as a Professor in the Department of Electronics and Communication Engineering, Coimbatore Institute of Technology, Coimbatore. She holds around 32 years of teaching experience. Her research interests are VLSI Design, Digital Image Processing and Digital Signal Processing. She is also guiding research scholars in different disciplines.

# A SMART SOLAR PV MONITORING SYSTEM USING IOT

V.Kavitha<sup>1</sup> and V.Malathi<sup>2</sup>

<sup>1</sup>PhD Scholar, Department of Electrical and Electronics Engineering, Anna University Regional Campus, Madurai, India

<sup>2</sup>Professor, Department of Electrical and Electronics Engineering, Anna University Regional Campus, Madurai, India

### ABSTRACT

Renewable energy sources are proven to be reliable and accepted as the best alternative for fulfilling our increasing energy needs. Solar photovoltaic energy is the emerging and enticing clean technologies with zero carbon emission in today's world. To harness the solar power generation, it is indeed necessary to pay serious attention to its maintenance as well as application. The IoT based solar energy monitoring system is proposed to collect and analyzes the solar energy parameters to predict the performance for ensuring stable power generation. The main advantage of the system is to determine optimal performance for better maintenance of solar PV (photovoltaic). The prime target of PV monitoring system is to offer a cost-effective solution, which incessantly displays remote energy yields and its performance either on the computer or through smart phones. The proposed system is tested with a solar module of 125-watts to monitor string voltage, string current, temperature, and irradiance. This PV monitoring system is developed by a smart Wi-Fi enabled CC3200 microcontroller with latest embedded ARM processor that communicates and uploads the data in cloud platform with the Blynk application. Also the Wireless monitoring system maximizes the operational reliability of a PV system with minimum system cost.

#### **Keywords**

Solar PV, Internet of Things, Mobile Application, Online Monitoring.

## **1. INTRODUCTION**

Power generation is a major factor in many developing countries. Due to the improvement of the industrial and commercial sector, energy demand reaches its peak. Hence all are poignant towards renewable energy source to produce green energy for meeting out our energy consumption. This can help the society to decrease greenhouse gas emission and ozone layer depletion for future generation. Among this solar photovoltaic technique is gaining popularity due to huge availability, reduced cost, easy installation, and maintenance. Currently, Internet of Things (IoT) is an evolving technology that makes things smarter and user-friendly when connected through the communication protocol and cloud platform. The efficiency of the solar panel is influenced by basic parameters such as current, voltage, Irradiance, and temperature. Hence real-time solar monitoring system is essential for increasing the performance of the PV panel by comparing with the experimental result to initiate preventive action. In recent years there had been a lot of research attempts made in solar energy. A simple forecasting database is modeled using MySQL to collect the raw data, filter un-relevant values and produce forecast without the assistance of any modern automation tools. In addition, machine intelligence techniques are used for forecasting to obtain robust performance [1]. A real-time supervising

N. Ramasubramanian et al.(Eds) : SRAIC-2019 pp. 01-33, 2019. © CS & IT-CSCP 2019

#### Computer Science & Information Technology (CS & IT)

and data acquisition model for Solar PV module is proposed using LABVIEW to determine the performance of different solar PV ratings. This is a powerful tool for exploring the operation of different PV modules with respect to real-time data [2-3]. Microcontroller based displaying system is proposed to monitor the different factors that affect the performance of PV panel. The measured parameters are evaluated with the standard operating condition to provide necessary action for better performance of PV [4].

A low-cost solar panel monitoring is developed based on IoT for online visualization and improving the performance. This helps to take preventive maintenance and tracking the fault location [5]. An IoT based cloud monitoring system is proposed and developed using the Raspberry pi for remote PV plant [6]. The basic characteristics of a PV system are analyzed using LABVIEW tool for real-time measurement to study the fault diagnosis in PV plant [7]. A smart monitoring system is developed with a microcontroller and Labview to gain the maximum efficiency with the use of sun trackers [8]. A remote Solar monitoring and control system is proposed for implementation at the plant level and promotes the decisional process for central control station which has the crucial role for processing, storage, warning and displaying [9].PV monitoring system is developed based on wired and wireless networks to transmit the parameters to a remote coordinator that offers a web-based application for remote access [10]. A practical graphical user interface is developed using Lab view for online monitoring for solar PV. Arduino controller is used for analyzing the measured parameters and sends the data to the server for making a useful decision which improves the performance of PV panel [11]. A costeffective smart architecture is proposed to optimize the efficiency of the PV panel by detecting the performance degradation through continuous monitoring system [12]. HEM algorithm based smart controller is implemented for choosing the source priority to maximize the use of Solar PV for home power management [17]. Therefore, the proposed work illustrate the real-time Solar PV monitoring system using cost efficient Smart Controller communicate with the cloud platform provides large storage space and fast dataaccess.

The paper is structured as follows: Section II describes the conventional work. Section III presents the proposed work and its functionality. Section IV illustrates the results of Solar monitoring system. Section V summarizes the proposed work and its application.

## 2. RELATED WORK

20

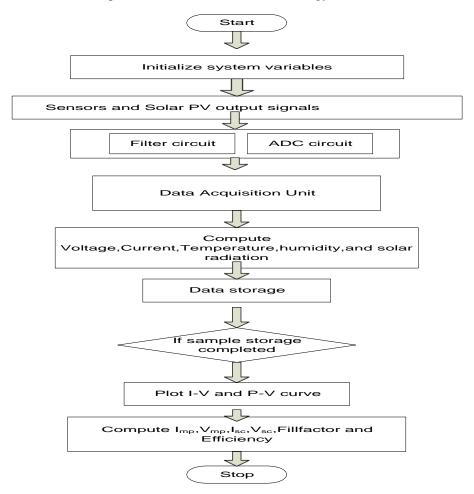

A virtually reliable Solar PV monitoring system [2] is developed with LABVIEW software is shown in Fig.1 a practical development tool for computing the performance of a 5-Watt Solar Module. The electrical parameters like voltage, current, temperature, humidity and irradiance are measured using sensors and store the data in the DAQ (Data Acquisition) unit, which provide an interface to the PC. LABVIEW tool plot the I-V and P-V graph based on the data acquired and also compute the Maximum voltage, Maximum current, Fill factor and efficiency of the solarpanel.

Figure.1 Virtual Solar PV monitoring system using LABVIEW

## **3. PROPOSED WORK**

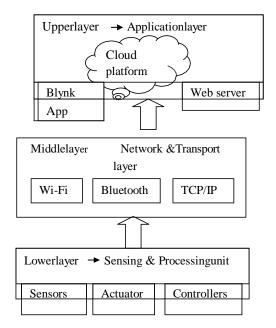

The real-time solar energy monitoring system is proposed based on the three-layer architecture of Internet of Things (IoT). The three-stage architecture is shown in Fig 2. The lower layer contains sensing and actuating devices like sensors, actuators, RFID, camera, and controllers since it is a combination of sensing and processing layer. The next layer is a middle layer which encompasses network layer with wired and wireless network like LAN, Bluetooth, Zigbee, 4G, Wi-Fi etc., act as a gateway to route the packets (data) to the transport layer that contains TCP/IP, UDP, for further transmission of data to the upper end. The final stage is the application layer deliver user interface and cloud platform for remote access.

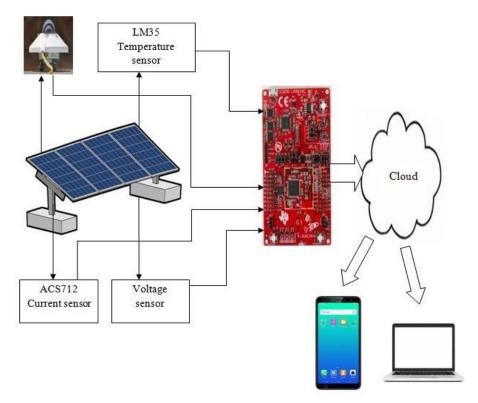

Figure.2 Three-layer architecture of Internet of Things

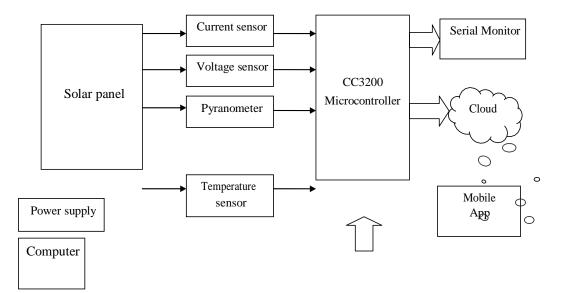

The block diagram of IoT based solar monitoring system is shown in Fig.3. This illustrates the outline of our proposed work. Poly Crystalline silicon of 125-watt solar panel is used for a monitoring system. The voltage and current sensors are used to measure the respective voltage and current from the panel. The temperature sensor is placed on the solar PV module to measure the current temperature which greatly affects the efficiency of the solar panel. Pyranometer is an instrument to measure the amount of solar irradiance in a planar surface in terms of  $W/m^2$ . The Microcontroller plays a pivotal role in handling the measured data for processing and forwards the data to the cloud platform through Wi-Fi module for concurrent observation and decision making.

Figure.3 Real-time Solar Energy Monitoring System

#### 3.1. Lower Layer

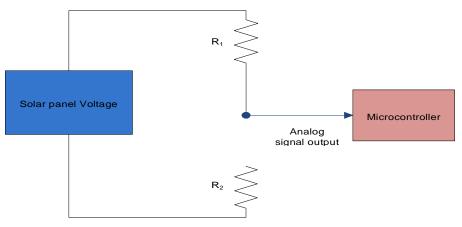

The sensing units are Voltage sensor, ACS 712 current sensor, pyranometer and temperature sensor. A voltage sensor is a divider circuit that can measure the voltage drop through series resistance. This circuit is useful for measuring voltage above 5 volts. The voltage is calculated based on the resistance factor and reference voltage. The voltage divider circuit is shown in Fig.4 The expression for calculating voltageis

*Voltage* = (*Analog value / Resistance Factor*)\* *Reference Voltage*

Resistance factor is calculated with the value of series resistance R1 and R2.

Figure.4 Voltage divider circuit

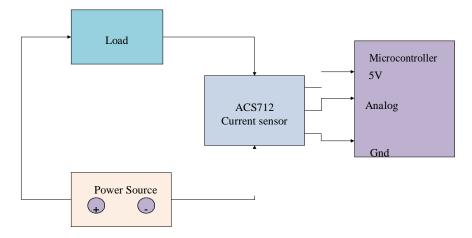

A current sensor used for measuring solar PV panel is the ACS712 Hall Effect sensor, which can measure up to 20 Amps. This can be effective to measure both DC and AC current. Hall effect sensor connects with the microcontroller through three terminals Analog input, power supply, and ground. The current sensor module is shown inFig.5

Figure.5 Schematic layout of the current sensor

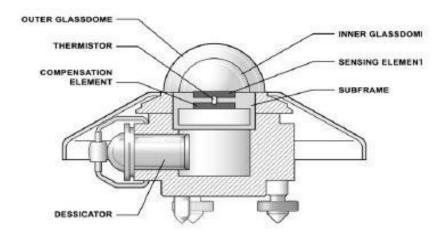

CM21 pyranometer shows high precision for measuring the solar radiance in a plane surface due to direct and diffused solar radiation. The high quality optical domes help to reduce the directional error less than 10 W/m2. It has high sensitivity for data acquisition system and provides low impedance for interference and noise. It has the maximum spectral range of 300-

1200 nm with sensitivity between 7 and 17  $\mu$ V/Wm<sup>-2</sup>. The operating temperature of this instrument is -40°C to +80°C.The construction of pyranometer [13] is shown in Fig.6. In general, the global radiation is determined using the output voltage of pyranometer and its sensitivity. For the calculation of solarirradiance

## $E = U_{emf} / Sensitivity$

24

E = solar irradiance in $W/m^2$

$U_{emf}=$  output voltage of pyranometer in  $\mu V$  Sensitivity =Sensitivity of pyranometer in  $\mu V/W/m^2$

Figure 6. The general structure of CM21 Pyranometer

The sensor for measuring the temperature of the solar panel is LM35 an analog sensor. It is a low cost, a tiny sensor to measure the environmental temperature from  $-50^{\circ}$ C to  $+150^{\circ}$ C. The operating voltage of this IC is 5v. There is an increase of 0.01v for all rise in temperature. The formula for converting the voltage to temperature is

#### $Temperature = Voltage / 10mV/^{\circ}C$

## CC3200 MICROCONTROLLER:

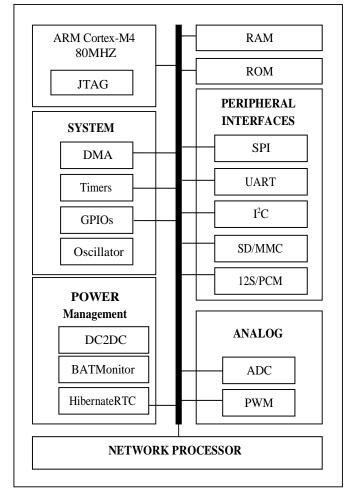

A CC3200 simple link is a system-on-chip (SoC) controller with inbuilt Wi-Fi connectivity designed for IoT Application. The wireless MCU (Microcontroller Unit) includes a high-speed ARM cortex M4 processor to develop a real-time application with the Single IC (Integrated chip). The controllers has embedded memory of 256KB RAM, serial Flash boot loader and ROMdrivers.TheMCUhas12-bitAnalog-to-Digital Converter(ADC) with four channels and 27 programmable general purpose input output (GPIO) pins. The Wi-Fi module contains 802.11b/g/n radio provides a fast and secure internet connection with advanced encryption standards. The power management subsystem includes a DC-DC converter to maintain a broad range of supply voltages. The Fig.7 shows [14] the hardware overview of the controller.

Figure 7. Hardware overview of CC3200

## 3.2. Middle Layer

In the middle layer, the smart controller processes the sensed data and transmits the information through Wi-Fi protocol which acts as a gateway to communicate with the upper end. The communication protocol like TCP/IP, UDP provides standard rules to ensure secure data transmission to the application layer.

## 3.3. Upper Layer

The Final layer is the application layer which can store the real-time data in a cloud platform for easier access, data visualization, and right decision making. This proposed work facilitates a cloud-based mobile application; Blynk [15] is used for tracking the operation of solar PV in real-time.

Blynk is a free source cloud platform offers user-friendly IoT application. We can develop a secure scalable and fast application with pre-designed elements to view the data virtually. It supports many hardware platforms and connectivity types for deploying any number of devices online. It gives a continuous solution for the remote application which saves time and resources with the very low cost.

# 4. RESULTS AND DISCUSSION

26

A polycrystalline 125-Watt photovoltaic module is taken for the experimental implementation and testing the performance with standard ratings of the solar panel as mentioned in Table 1. The proposed work is carried out in a solar energy testing center at Madurai Kamaraj University. The hardware setup is shown in Fig.8 and Fig.9. A high precision pyranometer is used to measure the solar radiance on a plane surface. LM 35 a sensing device to measure the current temperature in the solar panel. These two parameters highly influence the performance of the solar panel[16].

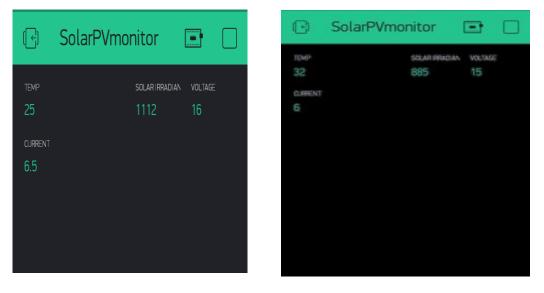

Since irradiance is corresponding to current and temperature affects the voltage of the solar module. Hence the power generation of the solar panel relies on temperature and irradiance. The proposed system programming codes are developed in C language via Energia IDE. This is a non-proprietary integrated development environment designed for Texas Instruments like CC3200 Microcontroller. The blynk libraries are included in the programming function to communicate and transfer the sensed values to the Cloud platform. The electrical characteristics are monitored and displayed successfully through a mobile application. The result in Fig.10 shows the real-time Solar PV monitoring system through Blynk. The inference of output is the increase in temperature reduces the voltage generation in PV and also the rise in irradiance shows a moderate increase in current. Hence these two parameters become the deciding factor for the performance of solar module. The results shown in Fig.11 are displayed in the Web server. The Fig.13 shows the output in serial monitor of PC. The obtained result is nearer to the Standard ratings of a solar panel.

Figure.8 Hardware implementation of proposed work

Figure.9 Experimental setup of Solar PV Monitoring System

Figure.10 Real-time Solar PV monitoring system using Blynk

# IoT based Solar PV Monitoring system

Temperature: 29\*C Irradiance: 903.50W/m2 Voltage: 16.04V Current: 6.29A Power: 100.88W

Fig.11(a)

27

# IoT based Solar PV Monitoring system

Temperature: 30\*C Irradiance: 902.00W/m2 Voltage: 15.79V Current: 6.29A Power: 99.37W

#### Fig.11(b)

Fig.11 (a-b) Solar PV Monitoring output through Web server

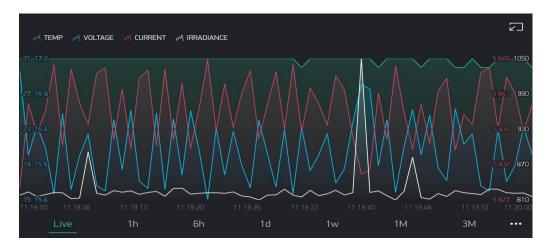

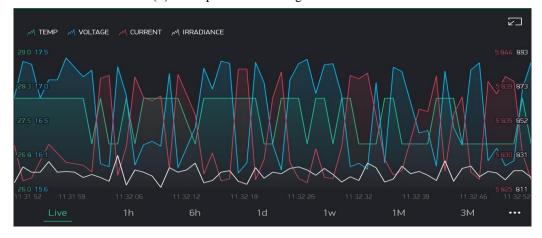

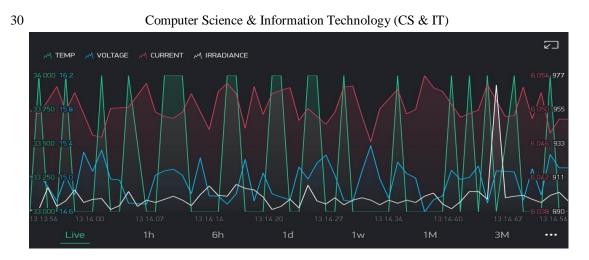

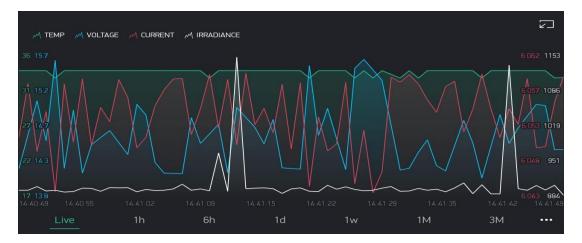

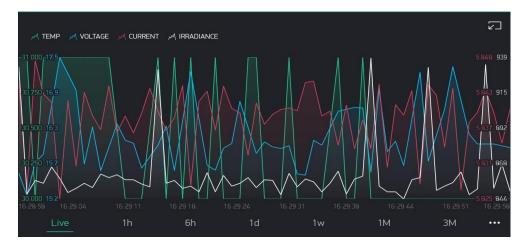

Fig.12 represents graph of solar power monitoring system through blynk application. The experiment is carried out for a week with different time intervals from 10.00AM to 05.00PM in a Solar Energy testing centre at Madurai, India. The electrical parameters of PV module are analyzed by continuous monitoring for estimating the behavior of solar panel. The graph shows the variation in temperature due to climatic condition which influences the voltage generation and irradiance affects the current parameter of PV module. The standard operating temperature of the solar panel is 25°C. Generally, the temperature above the standard test condition may reduce the performance of solar panel [16]. The decrease in temperature shows the rise in voltage as shown in Fig 12(a), (b), (c), (d), (e), (f) and the current directly correlate with irradiance. Hence, the change in solar radiation impacts the current characteristics in PV panel. The temperature reduces from 31°C to 30°C during morning hours from 10.30 AM to 11.30AM; the voltage goes to peak and then oscillates until reaching the stable state, at the instance irradiance is also maximum at this temperature which is shown in Fig.12 (a) and (b). The result of 12(c) represents the fall in temperature after 11.30AM and simultaneously the irradiance shows sharp reduction in spectral range. The Fig.12 (d) display the rise in temperature after 01.00 PM, at this stage irradiance level increase as current increases and the voltage generation reduces when there is a rise in temperature. The graph plotted in 12 (e) and (f) is observed after peak hours (i.e.) 02.00 PM to 05.00 PM. During the interval the temperature changes frequently from high to low and low to high and also solar radiation varies according to environmental condition. Hence the result shows the maximum power generation of solar panel which is nearly close to standard rating of PV.

(a) Solar power monitoring at 10.50AM

(b) Solar power monitoring at 11.20AM

29

(d) Solar power monitoring after 1.00PM

(e) Solar power monitoring after 2.00PM

(f) Solar power monitoring after4.00PM

Fig.12(a-f) Graphical view of solar energy monitoring system through blynk application

```

SMOD 🍯

```

| Temp: 27*C        |            |

|-------------------|------------|

| Voltage: 17.36V   |            |

| Current: 5.83A    |            |

| Solar irradiance: | 827.73W/m2 |

| Temp: 27*C        |            |

| Voltage: 16.88V   |            |

| Current: 5.83A    |            |

| Solar irradiance: | 824.55W/m2 |

| Temp: 27*C        |            |

| Voltage: 17.35V   |            |

| Current: 5.83A    |            |

| Solar irradiance: | 815.45W/m2 |

| Temp: 28*C        |            |

| Voltage: 17.37V   |            |

| Current: 5.83A    |            |

| Solar irradiance: | 814.09W/m2 |

| Temp: 27*C        |            |

| Voltage: 15.66V   |            |

| Current: 5.84A    |            |

| Solar irradiance: | 817.27W/m2 |

#### Fig.13 Solar PV Monitoring Output through Serial Monitor

| S.No | Electrical ratings                             | Value                |

|------|------------------------------------------------|----------------------|

| 1.   | Rated Maximum<br>power (P <sub>max)</sub>      | $125Wp \pm 3\%$      |

| 2.   | Open-Circuit<br>Voltage(V <sub>oc</sub> )      | 21.6 V               |

| 3.   | Short Circuit Current<br>(I <sub>sc</sub> )    | 7.66 A               |

| 4.   | Voltage at Maximum<br>power (V <sub>mp</sub> ) | 17.65 V              |

| 5.   | Current at Maximum<br>Power(I <sub>mp</sub> )  | 7.08 A               |

| 6.   | System voltage                                 | 1000V <sub>max</sub> |

Table.1 125-Watt Solar PV ratings

## 5. CONCLUSIONS

An IoT based virtual solar energy monitoring system is developed using a low-cost smart microcontroller. The cloud-based Blynk application shows the measured solar parameter in realtime through mobile. The monitored parameters show the optimized result that matches approximately with Electrical ratings of solar module tested under Standard Test Condition (STC). The proposed work helps to predict the performance of the Solar PV module through remote access. This can be extended for a large-scale solar plant to take preventive action by regularly monitoring the performance of the solar plant. It will be highly useful for the industrial and commercial application.

#### **ACKNOWLEGDEMENTS**

The authors want to thank the Head of the department of Solar Energy for carrying out this work in solar testing centre at Madurai Kamaraj University and colleagues for their remarkable comments to improve the work and assistance in proof reading.

## REFERENCES

32

- [1] Hugo T.C. Pedro, Edwin Lim, Carlos F.M. Coimbra(2018), "A database infrastructure to implement real-time solar and wind power generation intra-hour forecasts", *International Journal of Renewable energy Elsevier*, Vol.123,pp.513-525.

- [2] Amit Kumar Rohit, Amit Tomar, Anurag Kumar, Saroj Rangnekar(2017), "Virtual lab-based realtime data acquisition, measurement and monitoring platform for solar photovoltaic module", *International Journal of Resource-Efficient Technologies*, pp.1-6.

- [3] N.A. Othman, N.S. Damanhuri, I.R. Ibrahim, R. Radzali, M.N. Mohd (2010), "Automated Monitoring System for Small Scale Dual-Tariff Solar PV plant in UiTM Pulau Pinang", Proceedings of the World Congress on Engineering(WCE) U.K, Vol.2, pp.1-3.

- [4] Kangkana Hazarikaa, Pradyumna Kumar Choudhurya(2017), "Automatic monitoring of solar photovoltaic (SPV) module", Science direct proceedings Vol. 4, pp.12606–12609.

- [5] Soham Adhya, Dipak Saha, Abhijit Das, Joydip Jana, Hiranmay Saha (2016), "An IoT Based Smart Solar Photovoltaic Remote Monitoring and Control unit", IEEE International Conference on Control, Instrumentation, Energy & Communication (CIEC), pp.432-436.

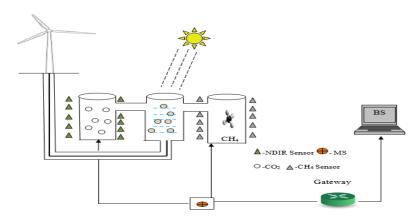

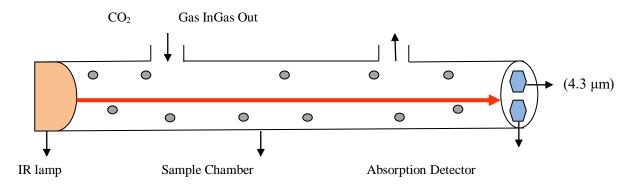

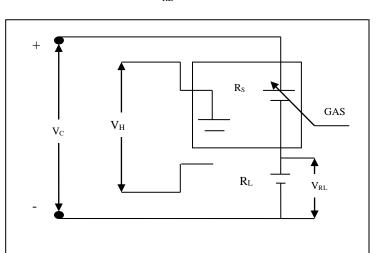

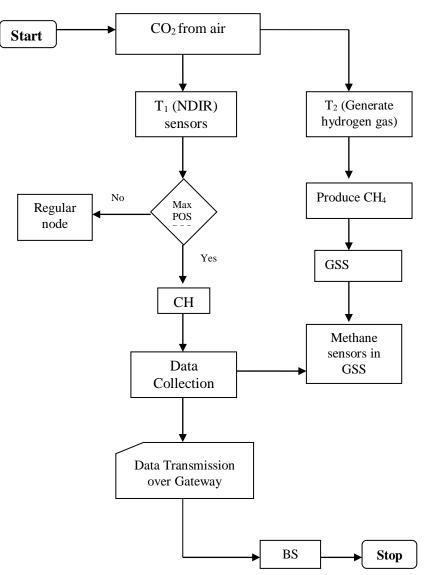

- [6] Renata I. S. Pereira, Ivonne M. Dupont, Paulo C. M. Carvalho, Sandro C. S. Juca (2017), "IoT Embedded Linux System based on Raspberry Pi applied to Real-Time Cloud Monitoring of a decentralized Photovoltaic plant", *International Journal of measurement Elsevier*, Vol.2, pp.1-18.

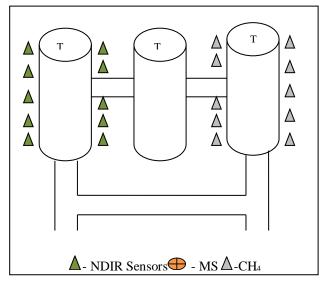

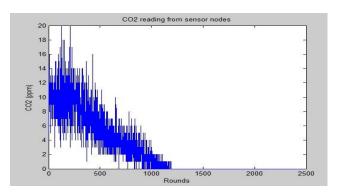

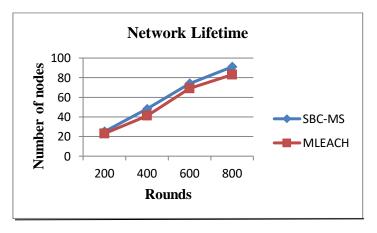

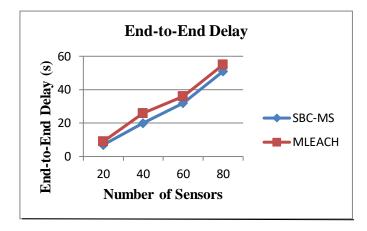

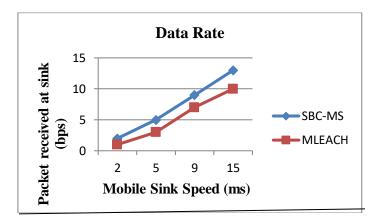

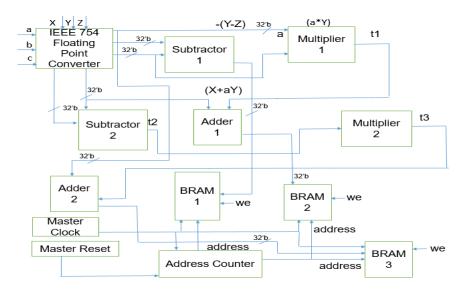

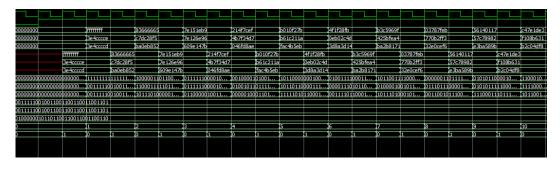

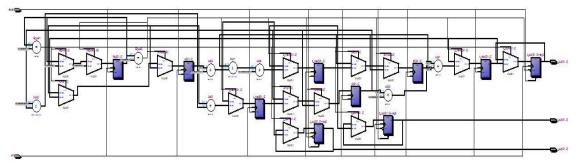

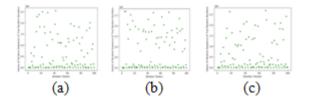

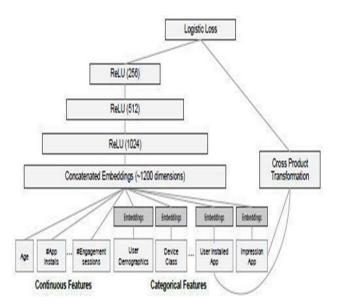

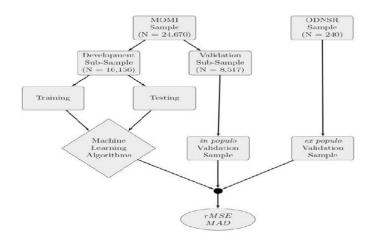

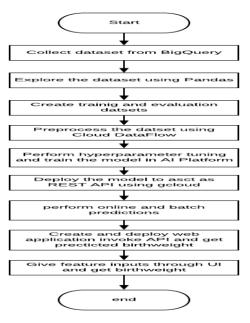

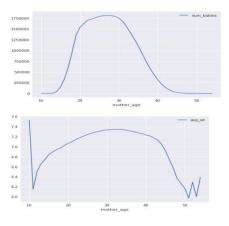

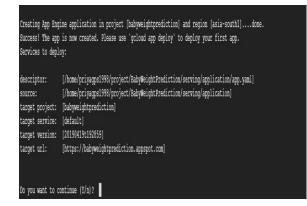

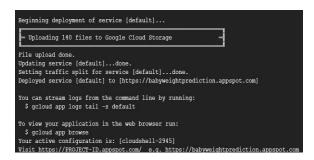

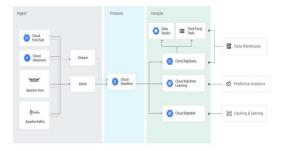

- [7] Aissa Chouder, Santiago Silvestre, Bilal Taghezouit, Engin Karatepe(2013), "Monitoring, modeling and simulation of PV systems using LabVIEW", *International Journal of Solar energy Elsevier*, Vol.1,pp.337-349.