# A NEW APPROACH TO DESIGN LOW POWER CMOS FLASH A/D CONVERTER

Sudakar S. Chauhan<sup>1</sup>, S. Manabala<sup>2</sup>, S.C. Bose<sup>3</sup> and R. Chandel<sup>4</sup>

<sup>1</sup>Department of Electronics & Communication Engineering, Graphic Era University, Dehradun, India

sudakarnith@gmail.com

<sup>2,3</sup>Central Electronics Engineering Research Institute (CEERI), Pilani, India santosh.manabala@gmail.com, bose.ceeri@gmail.com

<sup>4</sup>Department of Electronics & Communication Engineering, National Institute of Technology, Hamirpur, India

rchandel@nitham.ac.in

#### **ABSTRACT**

In the present paper, a 4-bit flash analog to digital converter for low power SoC application is presented. CMOS inverter has been used as a comparator and by adjusting the ratio of channel width and length, the switching threshold of the CMOS inverter is varied to detect the input analog signal. The simulation results show that this proposed 4-bit flash ADC consumes about 12.4 mW at 200M sample/s with 3.3V supply voltage in TSMC 0.35 µm process. Compared with the traditional flash ADC, this proposed method can reduce about 78% in power consumption.

#### KEYWORDS

CMOS Inverter, XOR gate based encoder, Flash ADC.

## 1. Introduction

With the rapid growth of modern communications and signal processing systems, handheld wireless computers and consumer electronics are becoming increasingly popular. Mixed-signal integrated circuits have a tendency in the design of system-on-chip (SOC) in recent years. SOC designs have made possible substantial cost and form factor reductions, in part since they integrate crucial analog interface circuits, such as ADCs with digital computing and signal processing circuits on the same die. The interfaces only occupy a small fraction of the chip die and for SOC designs, the technology selection and system design choices are mainly driven by digital circuit requirements. To limit energy in a reasonable size battery, minimum power dissipation in the mixed-signal integrated circuits is necessary [1]-[5]. The analog-to-digital converter (ADC) is the key components in modern electronics and becomes a part of the SOC products because it bridges the gap between the analog physical world and digital logic world. In the digital domain, low-power, low-voltage requirements are becoming important issues as the channel length of MOSFET shrinks below 0.35µm values [6]. Of all types of ADCs the flash ADC has not only high data conversion rate required for applications such as video and communication systems, but also it becomes the part of other types of ADCs viz. pipeline and multi bit sigma delta ADCs as well as no idle time for continuous data conversion [7]. However, the use of large no of analog comparators in flash ADC makes it a complex chip design and causes high power dissipation [8]-[10]. Furthermore both its area and power become a critical issue as the resolution is increased [11]-[13]. However along with speed both size and power are

DOI: 10.5121/vlsic.2011.2208 100 important design parameters for an ADC especially for SOC applications. In [1], bisection method is used to design low power CMOS flash ADC. In [2], multiple-section method is used to design low power CMOS flash ADC. In [7], Interpolation technique is proposed to reduce the no of preamplifiers, hence reducing the power dissipation in flash ADC. In [12], the focus is on low voltage and high speed design. In [13], an average termination circuit is proposed to reduce the no of over-range amplifiers, hence reducing the power consumption. In [15], the TIQ technique has been used to design a flash ADC. In [18], the entire ADC is implemented using current-mode logic (CML) blocks. In [19], a capacitive interpolation technique is employed for low power design which eliminates the need of resistor ladder. The present work is an attempt in this direction. In this paper, it is aimed to design a flash ADC with low power consumption by using CMOS inverter as a comparator rather than analog comparator. The results show that the circuit size and power dissipation can be efficiently reduced by this design.

## 2. Modified Flash Add

A traditional n-bit flash ADC architecture uses  $2^n$  resistors and  $2^{n-1}$  comparators to convert an analog signal to digital. This architecture has drawbacks like large input signal driving, high reference accuracy, high driving reference voltage and circuit complexity [10], [14]. CMOS inverters have been reported to be used in ADC designs [14]-[15]. In this work, this novel idea of employing CMOS inverters instead of analog comparators is considered for a flash ADC. CMOS is a combination of an n-MOSFET (NMOS) and a p-MOSFET (PMOS). CMOS inverter switching threshold ( $V_{th}$ ) is a point at which input is equal to output voltage ( $V_{in}$ = $V_{out}$ ) and in this region both PMOS and NMOS always operate in saturation region. If the input arrives at a particular threshold voltage, then the output state changes.  $V_{th}$  can be obtained as [14]-[15]

$$V_{th} = \frac{V_{DD} + V_{tp} + V_{tn} \left( K_{n} / K_{p} \right)^{\frac{1}{2}}}{1 + \left( K_{n} / K_{p} \right)^{\frac{1}{2}}}$$

(1)

where,

$$k_{n} = k_{n}' \frac{W_{n}}{L_{n}} \tag{2}$$

$$k_{p} = k_{p}^{'} \frac{W_{p}}{L_{p}} \tag{3}$$

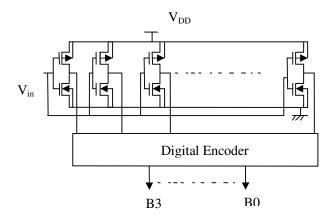

where  $k_n$  and  $k_p$  are constant transconductance parameters.  $V_{tn}$  and  $V_{tp}$  are the threshold voltage values of NMOS and PMOS respectively. As the voltages are constant,  $V_{th}$  depends on  $k_n$  and  $k_p$ values which decide the transition point of CMOS inverter [16]. If the ratio of  $k_n$  and  $k_p$  is decreased, the transited threshold voltage becomes high, otherwise, the transited inverter threshold voltage becomes low.  $k_n$  and  $k_p$  can be controlled by adjusting the width (W) and length (L) of NMOS and PMOS respectively. Based on this concept, various width/length ratio of CMOS inverters are designed to change their threshold voltages. Each CMOS inverter thus has a specified threshold depending upon this ratio. The W/L ratios are defined as  $Z_n=W_n/L_n$  and  $Z_p=W_p/L_p$ . By changing the ratio of  $Z_n$  and  $Z_p$ , we can obtain various transit threshold voltages of CMOS inverters to quantize the input level. All inputs of CMOS inverter are tied together to detect the analog input level. If the input arrives at a particular threshold voltage, then the output state changes. The basic architecture of the proposed flash ADC is shown in Figure 1. In a 4-bit ADC, 15 CMOS inverters are tied in parallel to detect the input signal level. The inverter output is array from MSB to LSB. For LSB bit, the Z<sub>n</sub>/Z<sub>p</sub> value should become small to increase the threshold voltage and for MSB bit, the  $Z_n/Z_p$  value should become large to decrease the threshold voltage [14].

Figure 1. The architecture of proposed ADC

The function of the inverter is similar to the comparator used in a conventional flash ADC. The proposed technique does not require resistors and analog comparator. Hence, circuit complexity and size are greatly reduced because the input signal is detected by changing the width/length ratio of CMOS inverter. Since CMOS inverter only dissipates the power during the state transition, the power consumption becomes very low and the inverter does not require high driving current because the inverter has very high input impedance. From the above detailed information, one can achieve 15 bits to present the detected result for analog input signal. These 15 bits are encoded into 4-bit digital output code with the help of XOR gate encoder [14], [18]. If the inverter array outputs are A15 to A1, we encode it with B3 to B0 where A15 and B3 are MSBs respectively. It is found that B3 is equal to A8 and B2 can be obtained with XOR of A4, A8 and A12. Further, it is found that B2 is a sub term of B1, and B1 is also the sub term of B0. The logic function can be given by

$$B3 = A8 \tag{4}$$

$$B2 = A4 \oplus A8 \oplus A12 \tag{5}$$

$$B1 = B2 \oplus A2 \oplus A6 \oplus A10 \oplus A14 \tag{6}$$

$$B0=B1 \oplus A1 \oplus A3 \oplus A5 \oplus A7 \oplus A9 \oplus A11 \oplus A13 \oplus A15 \tag{7}$$

First, we implement B2 with two XOR gates, then B1 is realized with the result of B2 & four XOR gates, and B1 is achieved with B1 and eight XOR gates. Thus the encoder is designed using 14 XOR gates.

## 3. SIMULATION RESULTS AND DISCUSSION

Firstly, a 4-bit flash ADC based on the Figure 1 architecture is designed in TSMC 0.35µm technology [13], [16]. The 4-bit ADC is realized using all digital circuitry and uses 15 CMOS inverters. Table 1 gives the features of the designed 4-bit flash ADC. The input ramp signal whose detectable voltage range is from 0.5V to 1.9 V in this design and supply voltage is 3.3V.

Table 1. Features of 4-bit ADC

| Supply Voltage    | 3.3 V          |  |  |

|-------------------|----------------|--|--|

| Process           | 0.35 μm        |  |  |

| Resolution        | 4-bit          |  |  |

| Input Range       | 0.5V~1.9V      |  |  |

| Max Speed         | 200MS/s        |  |  |

| Transistor Count  | 72             |  |  |

| Accuracy (DNL)    | 0.2LSB/-0.9LSB |  |  |

| Power Dissipation | 12.4mW         |  |  |

The 15 transition points of each inverter and its  $Z_n/Z_p$  ratio are listed in Table 2.

Table 2. The transition point of 15 inverters in a flash ADC

| Inverter | $Z_n/Z_p$ | $V_{th}\left(V\right)$ |

|----------|-----------|------------------------|

| Inv1     | 330.00    | 0.50                   |

| Inv2     | 41.79     | 0.60                   |

| Inv3     | 13.20     | 0.70                   |

| Inv4     | 7.39      | 0.80                   |

| Inv5     | 4.00      | 0.90                   |

| Inv6     | 2.48      | 1.00                   |

| Inv7     | 1.55      | 1.10                   |

| Inv8     | 1.08      | 1.20                   |

| Inv9     | 0.75      | 1.30                   |

| Inv10    | 0.534     | 1.40                   |

| Inv11    | 0.374     | 1.50                   |

| Inv12    | 0.26      | 1.60                   |

| Inv13    | 0.178     | 1.70                   |

| Inv14    | 0.122     | 1.80                   |

| Inv15    | 0.078     | 1.90                   |

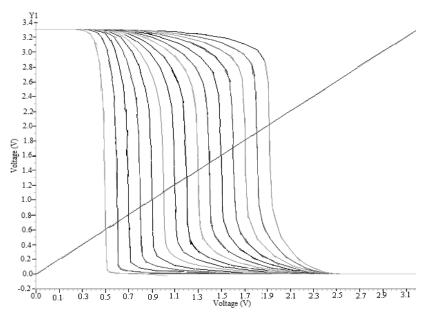

The detected step for input signal is about 0.1V by the change of the ratio of  $Z_n/Z_p$  of each inverter in experiments using (1). The DC transfer curves of 15 CMOS inverter are shown in Figure 2.

Figure 2. DC transfer curve of 15 CMOS inverters in the designed 4-bit ADC

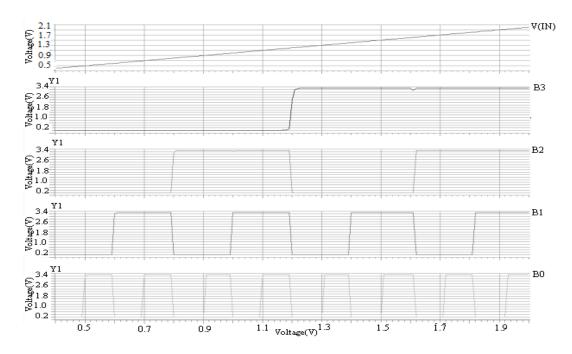

The input a linear ramp is also shown. SPICE simulations are carried out. Due to sub-channel effect and process variation, the  $Z_n/Z_p$  ratio must be adjusted to obtain a fixed step size. The outputs obtained at the inverters are given to the digital encoder using (4)-(7). Then the expected output digital binary code is achieved corresponding to the specified input voltage. Table 3 shows the relationship of analog input voltage and the output digital binary code. The 4-bit ADC core is simulated and the results are shown in Figure 3. The input signal is ramp waveform and the output is digital binary code as required. The maximum frequency of 200 MHz is achieved in 4bit flash ADC design. Differential non linearity (DNL) of an ADC is defined as a measure of separation between two adjacent codes measured at each vertical step in LSB. For a good design its value should be less than 1LSB [2], [19], [20]. Integral non linearity (INL) of the ADC is the maximum difference between the actual and ideal finite resolution characteristics measured vertically in LSB. For a good design its value should be less than 0.5LSB [20]. It is shown in Table 1 that the accuracy in terms of DNL is 0.2LSB/-0.9LSB and INL is 0.1LSB/-0.3LSB. Power dissipation of the ADC is 12.4 mW. Finally, the performance of the designed 4-bit ADC is compared for various parameters with results obtained in traditional flash ADC are presented in Table 4. Most of the flash ADCs use analog comparator to detect the input signal level. The power dissipation in proposed 4-bit flash ADC is 78% lesser than that of traditional flash ADC. Figure of Merit for the ADCs is taken as product of power and number of transistor count. Figure of merit of the proposed 4-bit ADC is 1.58 and is lowest compared to the traditional flash ADC as shown in Table 4. Therefore the proposed ADC is cost effective. As the CMOS inverter has high input impedance, hence our ADC design requires low input driving current and dissipates small power.

Table 3. Input range and outputs of 4-bit flash ADC core

| Input Signal (V <sub>in</sub> )                                           | Output Encoded Bits |    |    |    |

|---------------------------------------------------------------------------|---------------------|----|----|----|

|                                                                           | В3                  | B2 | B1 | В0 |

| 0.40V≤Vi< 0.51 V                                                          | 0                   | 0  | 0  | 0  |

| 0.51V≤Vi< 0.61 V                                                          | 0                   | 0  | 0  | 1  |

| 0.61V≤Vi< 0.71 V                                                          | 0                   | 0  | 1  | 0  |

| 0.71V≤Vi< 0.80V                                                           | 0                   | 0  | 1  | 1  |

| 0.80V≤Vi< 0.91V                                                           | 0                   | 1  | 0  | 0  |

| 0.91V≤Vi< 1.01 V                                                          | 0                   | 1  | 0  | 1  |

| 1.01V≤Vi< 1.11V                                                           | 0                   | 1  | 1  | 0  |

| 1.11V≤ Vi< 1.21V                                                          | 0                   | 1  | 1  | 1  |

| 1.21V≤Vi< 1.31V                                                           | 1                   | 0  | 0  | 0  |

| 1.31V≤Vi< 1.41V                                                           | 1                   | 0  | 0  | 1  |

| 1.41V≤Vi< 1.50V                                                           | 1                   | 0  | 1  | 0  |

| 1.50V≤Vi< 1.62 V                                                          | 1                   | 0  | 1  | 1  |

| 1.62V <vi< 1.72v<="" td=""><td>1</td><td>1</td><td>0</td><td>0</td></vi<> | 1                   | 1  | 0  | 0  |

| 1.72V≤ Vi< 1.82V                                                          | 1                   | 1  | 0  | 1  |

| 1.82V≤ Vi< 1.92V                                                          | 1                   | 1  | 1  | 0  |

| 1.92V≤ Vi< 2.03V                                                          | 1                   | 1  | 1  | 1  |

Figure 3. The simulation result of 4-bit ADC core

Table 4. Comparison of proposed flash ADC with traditional flash ADC

| Features          | Traditional    | Proposed       |

|-------------------|----------------|----------------|

| Power Supply      | 3.3 V          | 3.3V           |

| Process           | 0.35µm         | 0.35µm         |

| Resolution        | 4-bit          | 4-bit          |

| Sampling Freq     | 1 GS/s         | 200 MS/s       |

| DNL               | 0.2LSB/-0.3LSB | 0.2LSB/-0.9LSB |

| INL               | 0.2LSB/-0.3LSB | 0.2LSB/-0.5LSB |

| Transistor count  | 445            | 128            |

| Power Dissipation | 56.5 mW        | 12.4 mW        |

## 4. CONCLUSIONS

Low power architecture for a 4-bit CMOS inverter based flash ADC is presented using TSMC  $0.35\mu m$  technology. The proposed ADC design can achieve very low power dissipation and compared with the traditional flash ADC, this proposed method can reduce about 78% in power consumption as well as uses smaller silicon area. The DNL of the proposed ADC is within 0.2LSB/-0.9LSB and INL is within 0.2LSB/-0.5LSB. Figure of merit of the proposed 4-bit ADC is 1.58 and is lower compared to the traditional flash ADC, hence the proposed ADC is cost

effective. The proposed ADC chip so designed can be used for capacitive pressure sensor, video systems as well as it can be used in a low power two-step ADC, pipelined ADC and multi-bit sigma delta ADC.

#### ACKNOWLEDGEMENTS

The authors duly acknowledged with gratitude the support from Ministry of Communication & Information Technology, DIT Govt. Of India, New Delhi, through VLSI SMDP-II Project, CEERI Pilani Rajasthan and NIT Hamirpur HP, India.

### REFERENCES

- [1] C. Chun Tsai, Kai-Wei Hong, Yuh-Shyan Hwang, Wen-Ta Lee and Trong-Yen Lee, "New Power saving design method for CMOS flash ADC," The 2004 47th Midwest Symposium on Circuits and Systems, vol. 3. pp. 371-374, July 2004.

- [2] W. Ta Lee, P. Hsiang Huang, Y. Zhen Liao, and Y. Shyan Hwang, "A New Low-Power Flash ADC Using Multiple Section Method," IEEE Conference on Electron Devices and Solid-State Circuits, EDSSC 2007, pp. 341-344, 20-22 Dec. 2007.

- [3] M. Wang and C. H. Chen, "Design Synthesis and Performance Measurement of Pipelined Flash ADC for SoC Application", Proceeding of the 2005 IEEE Instrumentation and Measurement Technology Conference, pp.19-24, Ottawa, Ontario, Canada, USA, May 17-19, 2005.

- [4] M. Wang and C. H. Chen, "Architecture and Design Synthesis of 2.5 GS/s 4-bit Pipelined Flash ADC for SoC Application", Proc. Of the 31<sup>st</sup> Annual Conference of the IEEE Industrial Electronic Society, pp. 2224-2230, Raleigh, North Carolina, USA, Nov. 6-10, 2005.

- [5] A. Stojcevski, H. P. Le, J. Singh and A. Zayegh, "Flash ADC architecture", IEE Electronics Letters, vol.39, no.6, pp. 501-502, March 2003.

- [6] S. Banik, D. Gangopadhyay and T. K. Bhattacharyya, "A Low Power 1.8V 4-bit 400Mhz Flash ADC in 0.18 μm CMOS", Proc. Of the 19<sup>th</sup> International Conference On VLSI Design (VLSID'06).

- [7] C. W. Hsu and T. H. Kuo, "6-bit 500 Mhz Flash ADC with new design Techniques", IEE Proc. Circuits Devices Syst., vol.150, no.5, pp. 460-464, Oct. 2003.

- [8] W. Song, H. Choi, S. Kwak and B. Song, "A 10-bit 20MS/s Low Power CMOS ADC", IEEE J. Solid-State Circuits, vol. 30, pp. 514-520 May 1995.

- [9] G. M. Yin, F. Eynde and W. Sansen, "A High Speed CMOS Comparator with 8-bit Resolution", IEEE J. Solid-State Circuits, vol. 27, pp. 208-211, Feb. 1992.

- [10] V. Ferrazina, N. Ghittori and F. Maloberti, "Low Power 6-bit Flash ADC for High Speed Data Converters Architectures", IEEE Symposium on Circuits and Systems, pp. 3930-3933, 2006.

- [11] M. Choi and A. A. Abidi, "A 6-bit 1.3GS/s A/D converter in 0.35μm CMOS," IEEE Journal of Solid-State Circuits, vol.36, Dec.2001, pp. 1847-1858.

- [12] K. Uyttenhove and M. S. J. Steyaert, "A 1.8-V 6-bit 1.3 GHz flash ADC in 0.25µm CMOS" IEEE Journal of Solid-State Circuits, vol.38, July 2003, pp. 1115-1122.

- [13] P. C. S. Scholtens and M. Vertregt, "A 6-bit 1.6 GS/s Flash ADC in 0.18 μm CMOS using Averaging Termination", IEEE Journal of Solid-State Circuits, pp. 1599-1609, 2002.

- [14] S. Chang Hsia, Wen- Ching Lee, "A Very Low Power Flash A/D Converter Based on CMOS Inverter Circuit," IDEAS'05, pp. 107-110, July 2005.

- [15] A. Tangel and K. Choi, "CMOS Inverter as a comparator in ADC design," in Proc. ICEEE, 2001, pp. 1-5.

- [16] S. M. Kang and Y. Leblebici, CMOS Digital Integrated Circuits Analysis and Design, Tata McGraw-Hill Edition 2003.

- [17] S. Akiyama and Takao Waho, "A 6-bit Low-Power Compact Flash ADC Using Current-Mode Threshold Logic Gates." IEEE Symposium on Circuits and Systems, pp. 3938-3941, 2006.

- [18] S. Sheikhaei, S. Mirabbasi and A. Ivanov, "A 4 bit 5 GS/s Flash ADC in 0.18 µm CMOS", IEEE Symposium on Circuits and Systems (ISCAS), pp. 6138-6141, May 2005.

- [19] C. Sander, M. Clara, A. Santner, T. Hartig and F. Kuttner, "A 6-bit 1.2 GS/s Low Power Flash ADC in 0.13 μm CMOS", IEEE Journal of Solid-State Circuits, vol. 40, no. 7, pp. 1499-1505, July 2005.

- [20] D. A. Johns and K. martin, Analog Integrated Circuit Design, John Wiley & Sons 2002.

#### Authors

Sudakar S. Chauhan received M.Tech degree in VLSI Design Automation and Technique from National Institute of Technology, Hamirpur, India in 2009 and B.Tech degree in Electronics and Communication Engg.

from Graphic Era Institute of Technology, Dehradun, India in 2005. During 2008-2009, he stayed in Central Electronics Engineering & Research Institute, Pilani as a project trainee. Currently he is Asst. Prof. in Graphic Era University, Dehradun.

**S. Manabala** received MS degree IIIT Pune in 2007 and B.Tech degree in Electronics and Communication Engineering from BPUT, Orissa in 2004. Currently he is working in IC Design Group of Central Electronics Engineering Research Institute, Pilani, Rajasthan, India.

**Dr. S. C. Bose** received Ph.D. degree from KU. Currently he is Scientist F in IC Degign Group of Central Electronics Engineering Research Institute, Pilani, Rajasthan, India.

**Dr. R. Chandel** received Ph.D. degree in VLSI Design, Microelectronics from IIT Roorkee in 2005, M.Tech in Integrated Electronics from IIT Delhi in 1997 and B.Tech in Electronics and Comm.

From Thapar Institute of Engineering & Technology, Patiala in 1990. Currently she is an Associate Professor at NIT Hamirpur, India.

.