# PERFORMANCE EVALUATION OF CDMA ROUTER FOR NETWORK - ON - CHIP

Anant W. Hinganikar<sup>1</sup>, Mahendra A. Gaikwad<sup>2</sup> and Rajendra M. Patrikar<sup>3</sup>

<sup>1</sup>Department of E&T, B.D.College of Engineering, Sevagram (Wardha)-India anant.hinganikar@yahoo.com

<sup>2</sup>Department of EC, B.D.College of Engineering, Sevagram (Wardha)-India gaikma@rediffmail.com

<sup>3</sup>Department of EC, VNIT), Nagpur-India

Rajendra@computer.org

#### Abstract

This paper presents the performance evaluation of router based on code division multiple access technique (CDMA) for Network-on-Chip (NoC). The design is synthesized using Xilinx Virtex4 XC4VLX200 device. The functional behavior is verified using Modelsim XE III 6.2 C. The delay and throughput values are obtained for variable payload sizes. Throughput-Power and Delay-Power characteristics are also verified for NoC.

# **Keywords**

CDMA, Walsh Code, Router, NoC

#### 1. Introduction

Traditionally, ICs have been designed with dedicated point-to-point connections, with one wire dedicated to each signal. Now with new developments in chip manufacturing technologies several Intellectual Property (I.P.) blocks such as processor cores, memories, dedicated hardware can be built on single chip with high increase in computation performance. For such rising computation performance the communication bandwidth requirement also increases with same rate.[1][3]

The traditional bus based system is not suitable for communication, among these increasing onchip resources. The wires occupy much of the area of the chip and wiring delays are becoming dominant over gate delays. [4][5]. Networks are generally preferable to such buses because they have higher bandwidth and support multiple concurrent communications. [6]

Network-on-Chip (NoC) is an approach to designing the communication subsystem IP-cores in a System-on-Chip (SoC). NoC applies networking theory and methods to on-chip communication and brings notable improvements over conventional bus and crossbar interconnections. NoC improves the scalability of SoCs. Network-on-Chip (NoC) is an emerging paradigm for communications within large VLSI systems implemented on a single silicon chip. Network-on-Chip is spreading rapidly with the development of new architectures and new efficient routing techniques.

Although NoCs borrows the concepts and techniques from the well-established domain of computer networking, it is impractical to blindly reuse features of classical computer networks. With NoC-

DOI: 10.5121/vlsic.2012.3307

- [i] It is possible to take advantage of part of the technology developed for packet switched networks in the field of communication theory and computer networks, adapting those concepts to the particular constraints of on chip interconnection.

- [ii] It is possible to achieve a very high grade of flexibility.

- [iii] It is possible to make design modular by extensive use of parameterized independent functional blocks.

- [iv] Functional blocks can be reconfigured by mutually connecting them in different manners in order to create particular topology needed for a given application.

- [v] It is possible to easily integrate IP cores developed by different people or companies, provided that this modules share a common interface for communication with the external environment.

- [vi] Computing and communication environments are separated.

We have proposed a NoC router based on CDMA technique. Mostly the CDMA technique is widely used in wireless communication but some researchers have proposed various ways of applying CDMA technique for on chip wired communication. We have proposed the packet switched CDMA router which handles the issues - flow control and contention resolution. The rest of the paper is organized as follows. Section 2 gives brief idea about CDMA technique. Section 3 deals with the architecture of CDMA router. Synthesis results are summarized in section 4. Finally conclusion is drawn in section 5.

# 2. CDMA Technique

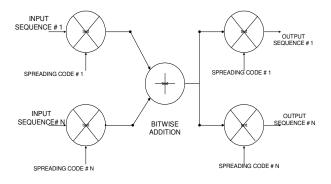

CDMA is a spread spectrum technique that uses a set of orthogonal codes to encode the input sequence from different sources before transmission. The encoded data from different senders are added together for transmission without interfering with each other, which is achieved by the orthogonal property of spreading code. The orthogonal property means normalized autocorrelation and cross correlation values of spreading codes are 1 and 0 respectively. Auto correlation of spreading codes refers to the sum of the product of codeword with itself whereas cross correlation refers to the sum of product of two different codewords.

At the receiving end the data can be decoded from received sum signals by multiplying the received signals with spreading codes used for encoding. This is possible because of the orthogonal property of spreading codes.

Figure 1. CDMA Communication

#### 3. CDMA Router Architecture

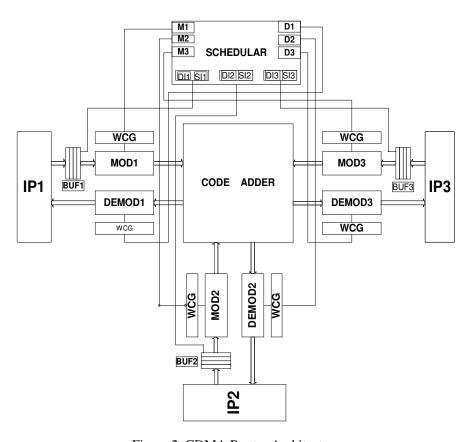

The CDMA router using three IP cores is shown in figure 2.Router architecture consists of six basic functional blocks- FIFO Buffer (BUF), Walsh Code Generator (WCG), Scheduler, Modulator (MOD), Code Adder, and Demodulator (DEMOD). The input packets from different IP Cores are stored in FIFO buffer of depth four. The packet consists of two-bit destination address, two-bit source address and a variable length payload. The two-bit source address is also transmitted to the destination along with the payload.

We have used Walsh code of length four as a spreading code for modulation. Each resource is assigned a fixed source address and corresponding fixed Walsh code as indicated in Table 1.

| Resource   | Source Address | Walsh Code |

|------------|----------------|------------|

| (Reserved) | 00             | 0000       |

| IP1        | 01             | 0101       |

| IP2        | 10             | 0011       |

| IP3        | 11             | 0110       |

Table 1. Walsh Codes assigned to resources

The all zero Walsh Code is reserved for the condition when there is no data to transmit with the resource. The Walsh code is generated from the source address. The router design is scalable as by selecting the Walsh code of higher length, number of IP cores attached to the router can be increased.

Figure 2. CDMA Router Architecture

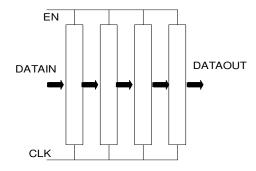

## 3.1 FIFO Buffer

The input buffering is used in the design. The length of the buffer is equal to the packet size and it is having a depth of four that holds four packets. When clock and enable are at logic high, the complete input packet is shifted to next memory slot. Thus minimum four clocks are required for the packet to come out of the buffer.

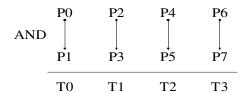

Figure 3. FIFO Buffer

## 3.2 Scheduler

Contention resolution is an important task in router. If two or more resources are sending data to one destination at same time then there is contention for destination. This contention is resolved by assigning priorities to the resources based on different requirements. Since we have implemented the router for three resources there can be contention for destination due to maximum of two resources. The scheduling algorithm is designed by observing different conditions for contention. All the possible conditions for contention are summarized in Table 2.

| case | source | destination | Contention |  |

|------|--------|-------------|------------|--|

|      | 01     | 10/11       |            |  |

| 1    | 10     | 01          | D1         |  |

| 1    | 11     | 01          | D1         |  |

|      | 01     | 10          |            |  |

| 2    | 10     | 01/11       | D2         |  |

| 2    | 11     | 10          | D2         |  |

|      | 01     | 11          |            |  |

| 2    | 10     | 11          | D2         |  |

| 3    | 11     | 01/10       | D3         |  |

|      | 01     | 10/11       | No         |  |

| 4    | 10     | 11/01       | Contention |  |

| 4    | 11     | 01/10       |            |  |

Table 2. Conditions for contention

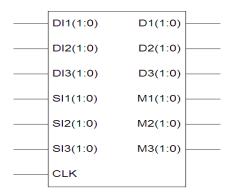

Figure 4. Conceptual Diagram of Scheduler

Figure 4 shows the conceptual diagram of scheduler. The four bit headers from all the resources which include two bit source address and two bit destination address are input to the scheduler. As per the scheduling algorithm, scheduler outputs source addresses and destination addresses to the Walsh Code Generators both at source and destination sides.

## 3.3 Walsh Code Generator

The Walsh code possesses the orthogonal and balance property which is essential for the CDMA communication. The Balance Property of Walsh code indicates equal number of 1's and 0's in the code.

Table 3. Truth table for Walsh Code Generation

| INPUT |    | OUTPUT |    |    |    |

|-------|----|--------|----|----|----|

| S0    | S1 | W0     | W1 | W2 | W3 |

| 0     | 0  | 0      | 0  | 0  | 0  |

| 0     | 1  | 0      | 1  | 0  | 1  |

| 1     | 0  | 0      | 0  | 1  | 1  |

| 1     | 1  | 0      | 1  | 1  | 0  |

Table 3 indicates truth table for generation of Walsh Code of length four from two bit source addresses.

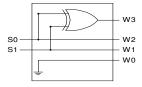

Figure 5. Walsh Code Generator

Figure 5 indicates the circuit realized from the truth table which is used for the generation of Walsh Code.

## 3.4 Modulator

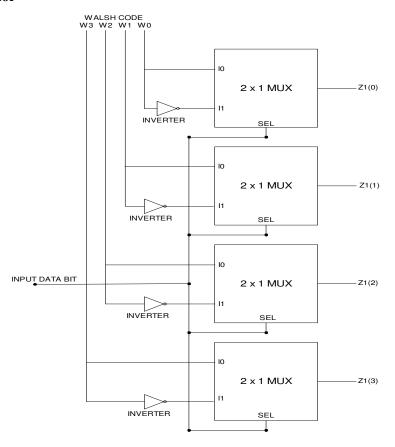

Figure 6. Modulator for 1 Bit

Figure 6 indicates the modulator for one bit. The four bit Walsh Code from Walsh Code Generator is assigned to the four MUXes as indicated in figure. Data bit is assigned to the select line of all the four MUXes. Modulation is carried out in parallel. The pseudo code of modulation algorithm is given bellow.

```

IF (data bit = = 0) THEN

{ Transmit Codeword Itself }

EISIF (data bit = = 1) THEN

{ Transmit Inverted Codeword }

END IF

```

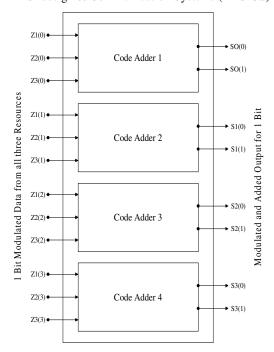

## 3.5 Code Adder

The modulated data bits from all the three resources are added together in code adder. This added data is transmitted to the demodulators of all the three resources simultaneously in parallel.

Figure 7 shows the code adder for 1 bit data from all the three resources.

Figure 7. Code Adder for 1 Bit

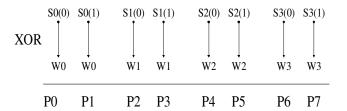

## 3.6 Demodulator

The modulated and added data is simultaneously sent to the demodulators of all the three resources. The data intended for particular demodulator is recovered with the help of Walsh Code. The demodulation algorithm is illustrated bellow. The demodulation is carried out in completely parallel manner. The demodulation algorithm given bellow decodes 1 bit of data. The algorithm is used in parallel to decode all the data bits.

Step 1:

Step 2:

Step 3:

## 4. SYNTHESIS RESULTS

The CDMA NoC router architecture was synthesized on Xilinx Virtex4 XC4VLX200 device with the FF1513 package and the -10 speed grade. The functional behavior of CDMA router architecture was verified using Modelsim XE III 6.2 C.

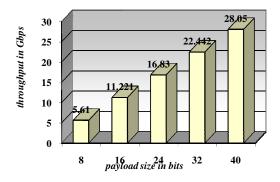

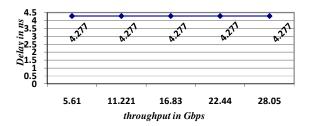

Table 4 summarizes the optimal frequency and total delay for various payload sizes. The total delay is distributed in logic and route delay. The delay is constant for variable range of payload.

| Payload<br>Size | Optimal<br>Frequency | Throughput  | Total<br>Delay | Logic -         | - Route         |

|-----------------|----------------------|-------------|----------------|-----------------|-----------------|

| 8 Bit           | 233.781 MHz          | 5.610 Gbps  | 4.277 ns       | 1.485 ns(34.7%) | 2.793 ns(65.3%) |

| 16 Bit          | 233.781 MHz          | 11.221 Gbps | 4.277 ns       | 1.485 ns(34.7%) | 2.793 ns(65.3%) |

| 24 Bit          | 233.781 MHz          | 16.83 Gbps  | 4.277 ns       | 1.485 ns(34.7%) | 2.793 ns(65.3%) |

| 32 Bit          | 233.781 MHz          | 22.442 Gbps | 4.277 ns       | 1.485 ns(34.7%) | 2.793 ns(65.3%) |

| 40 Bit          | 233.781 MHz          | 28.05 Gbps  | 4.277 ns       | 1.485 ns(34.7%) | 2.793 ns(65.3%) |

Table 4. Synthesis Results

Since the complete communication is in parallel the throughput is computed as (3 Resources) \*(Number of payload bits)\*(Clock Frequency). [2] The throughput values are obtained in Gbps.

Figure 8 shows throughput for different payload sizes. Since overall delay is constant and hence the optimal frequency, throughput is found to be the function of number of payload bits by keeping number of resources constant.

Figure 9 shows delay for different values of computed throughput. The delay is constant for all the values of throughput.

Figure 8. Payload Vs Throughput

Figure 9. Throughput Vs Delay

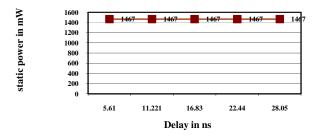

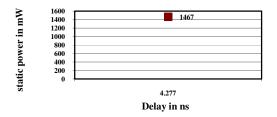

Figure 10 and 11 gives throughput-Power and Delay-Power characteristics

Figure 10. Throughput Vs Static Power

Figure 11. Delay Vs Static Power

# 5. CONCLUSION

The proposed CDMA is scalable, modular and reusable which satisfies the basic requirements of NoC. In the proposed CDMA router scheme for NoC it has been observed that delay is constant for various ranges of payloads. The concurrent transmission of data increases overall throughput.

## REFERENCES

- [1] Daewook Kim, Manho Kim and Gerald E. Sobelman, "CDMA Based Network On Chip Architecture" in *IEEE Asia Pacific Conference on Circuits and Systems*, pp. 137–140, 2004.

- [2] Daewook Kim, Manho Kim and Gerald E. Sobelman, "Design of high performance scalable CDMA router for on-Chip Switched Network" in *ISSOC*, 2005, pp.32–35.

- [3] Tatjana Nikolić, Goran Djordjević, and Mile Stojčev, "Simultaneous data transfers over peripheral bus using CDMA Technique" in 26th international conference on Microelectronics, IEEE conference publications, 2008 On page(s): 437.

- [4] Ankur Agarwal, Florida Atlantic University, Boca Raton, Cyril Iskander, Hi-Tek Multisystems, Canada, Ravi Shankar, Florida Atlantic University, Boca Raton, "Survey of Network on Chip (NoC) Architectures & Contributions" in the journal of Engineering Computing and Architecture ISSN 1934-7197 Volume 3, Issue 1, 2009.

- [5] Jun Ho Bahn, Seung Eun Lee and Nader Bagherzadeh, "On Design and Application Mapping of a Network-On-Chip (NoC) Architecture" in *Parallel Processing Letters*. 01/2008; 18:239-255.

- [6] William J. Dally and Brian Towles, "Route Packets Not Wires-On-Chip Interconnection Network" DAC 2001, June 18-22, 2001, Las Vegas, Nevada, USA.

- [7] Xin Wang, Jari Nurmi "An On-Chip CDMA Communication Network" in *Proceedings International Symposium on System-on-Chip*; 12/2005.

- [8] Ryuji Yoshimura, Tan Boon Keat, Toru Ogawa, Shingo Hatanaka, Toshimasa Matsuoka, Kenji Taniguchi "DS-CDMA Wired Bus with Simple Interconnection Topology for Parallel Processing System LSIs" in *IEEE International Solid-State Circuits Conference*, pp. 370–371, Feb. 2000.

- [9] Manho Kim, Daewook Kim and Gerald E. Sobelman, "Adaptive Scheduling for CDMA-Based Networks-on-Chip" in *IEEE-NEWCAS Conference*, *The 3rd International*; 07/2005.

- [10] Ik-Jae Chun, Tae-Moon Roh, and Bo-Gwan Kim, "Binary-Truncated CDMA-Based On-Chip Network" in *IEEE International Symposium on Circuits and Systems(ISCAS)*, pp. 397-400, 2007

- [11] Daewook Kim, Manho Kim and Gerald E. Sobelman, "FPGA- based CDMA Switch for Networks-on-Chip" in 13th IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2005), 17-20 April 2005, Napa, CA, USA, Proceedings; 01/2005.

- [12] Erno Salminen, Ari Kulmala, and Timo D. H"am"al"ainen "Survey of Network-on-chip Proposals" a White Paper, OCP-IP, MARCH 2008.

- [13] Xin Wang, Tapani Ahonen, and Jari Nurmi 'Applying CDMA Technique to Network-on-Chip" in *IEEE transactions on very large scale integration (VLSI) systems, Vol.15, NO. 10, October 2007.*

- [14] Shashi Kumar, Axel Jantsch, Juha-Pekka Soininen, Martti Forsell, Mikael Millberg, Johny Öberg1, Kari Tiensyrjä and Ahmed Hemani, "A Network on Chip Architecture And Design Methodology" in *IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, pp. 105-112, 2002.

- [15] Jun Ho Bahn, Seung Eun Lee and Nader Bagherzadeh "Design Of Router for Network on Chip" in *International Journal on High Performance System Architecture, Vol. 1, No.2, 2007.*

- [16] XinWang and Jari Nurmi "Comparison of a Ring On-Chip Network and a Code-Division Multiple-Access On-Chip Network" in *Hindawi Publishing Corporation, VLSI Design Volume 2007, Article ID 18372, 14 pages.*

- [17] Israel Cidon and Idit Keidar, "Zooming in on Network-on-Chip Architectures" in *Technion Department of Electrical Engineering, Tech. Rep. CCIT 565, Dec. 2005.*

#### **Authors**

Anant W. Hinganikar did his BE in Electronics Engineering in 2005 from Nagpur university. He completed his M. Tech from Bapurao Deshmukh College of Engineering, Sevagram, Nagpur University. Currently he is working as a Assistant Professor in the department of Electronics and Telecommunication Engineering, Sevagram (Wardha). He is a life member of Indian Society for Technical Education.

Mahendra A. Gaikwad did his BE in Electronics Engineering in 1991 from Nagpur University. He did his MBA in Marketing Management from Nagpur University and he has completed his MCM from Nagpur University. He did his Master's Degree in Personal Administration from Nagpur University. He did his M.Tech in Communication Engineering from Indian Institute of Technology, Bombay in 1998.

He has completed his PhD on "Network -on-Chip architecture using Perfect Difference Network Topology" at VNIT, Nagpur in 2012. Currently he is working as Professor and Dean (R&D) at Bapurao Deshmukh College of Engineering, Sewagram (Wardha).

He is the life member of professional bodies like Indian Society for Technical Education, Institution of Engineers (India), Indian Society for Telecommunication Engineers. He is also invitee member of Institution of Engineers (India), Nagpur local Chapter, Nagpur. He is also the member of Computer Society of India

Dr.Rajendra Patrikar did his M.Sc. in Physics from Nagpur University. He did M.Tech in Electrical Engineering from IIT Bombay. He joined as Research engineer in the Microelectronics Project at IIT Bombay. He completed his PhD from the same department. He joined as faculty at IIT Bombay after working for a year at Computer vision R&D Pune. Later he moved to Singapore to work in TECH Semiconductor in Advance Device Technology

After working there for three years he moved Institute of High Performance Computing Singapore where he carried research work in the area of CAD for VLSI and nano-electronics. He has published about 30 papers International Journals, international conferences and also filed one patent in USA in the area of VLSI Currently he is working as a professor & Dean (academic) at VNIT Nagpur.