# PERFORMANCE AND ANALYSIS OF ULTRA DEEP SUB MICRON TECHNOLOGY USING COMPLEMENTRY METAL OXIDE SEMICONDUCTOR INVERTER

Shikha Goswami<sup>1</sup> and Shyam Akashe<sup>2</sup>

<sup>1</sup>Research Scholar M.tech VLSI, ITM University, Gwalior, M.P <sup>2</sup>Associate Professor of Department of Electronics and Communication Engineering, I.T.M University, Gwalior, M.P

## ABSTRACT

CMOS technology had attained remarkable to progress and advances thus this progress had been achieved by certain downsizing of the MOSFETs. The dimension of the MOSFETs were scaled upon by factor which has historically found to be 0.7 in very large scale integration technology, power and delay analysis have become crucial design concern. In this paper we emphasize the comparative study of delay, average power and leakage power of CMOS inverter in Ultra Deep Submicron Technology range. This study shows variation of following as follows by delay to UDSM technology and also for average power and leakage power by diminishing to certain technology. The simulation results are taken for 45nm in Ultra Deep Submicron Technology range with the help of Cadence Tool and also analyzing the effect of load capacitance, transistor width and supply voltage on average power and delay of CMOS inverter of 45nm technology. Therefore the analysis has done with the aim to observe about the certain variation in delay and power with variation in transistor width in UDSM CMOS inverter and also had variation in load capacitance and supply voltage had been studied

## **KEYWORDS**

UDSM, CMOS Inverter, Average Power, Delay, Leakage Power.

# **1. INTRODUCTION**

The performance of the circuit can be enhanced by scaling MOSFETs to smaller dimension, which also reduces the space complexity. The dimension normally refers to the channel length of the transistor. The key process that defines the minimum dimension in a technology, eventually led to channel length below 1 urn, referred to submicron era. After this we had gone another scaling limit and will below .35um barrier, referred to Deep submicron (DSM) era. Scaling continued its relentless pace and then we entered a new era, where the minimum features of MOSFETs are being shifted to dimension below Deep submicron, so called Ultra Deep Submicron (UDSM) technology. The important challenges in this generation of IC designing is the increase in power dissipation in the circuit which reduces the battery -power, it also effect the reliability of the circuit due to interconnect aging process and accelerated device.[I] The major

DOI: 10.5121/vlsic.2014.5608

advantage of power analysis is the battery life of equipment is directly related to power dissipation. Delay analysis also has importance in synthesis of VLSI design. Integrated circuit designer have constantly sought accurate and effect delay evaluation technique that will variety of option and better utilize the design space [2]. There are different secondary effects like body bias effect, channel length modulation effect, velocity saturation effect, drain induced barrier lowering (DIBL) etc which will modify power and delay models [3]. The most popular delay model in DSM range is described I nth power law [4]. , Where velocity saturation is main consideration. This paper represents simulation of CMOS inverter by considering MOSFET's channel length 45nm technology for UDSM range. The result shows how the leakage power, average power and delay depend on different design parameter for DSM and UDSM technology.

This paper organized in such a way that, after the description of UDSM technology MOSFET in section I, section II and section III contain brief description of delay and power modelling of CMOS Inverter. Simulation results and analysis are mentioned in section IV; section V includes summary and conclusion.

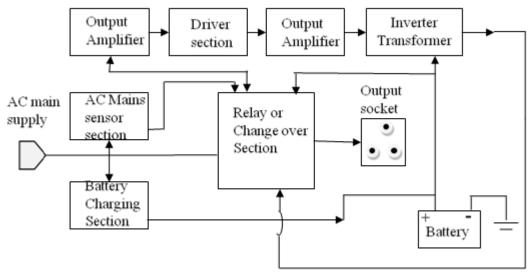

Figure 1: Block diagram of inverter

## 2. DELAY EXPRESSION FOR CMOS CIRCUIT

Using nth power law [4], the delay model of CMOS inverter can be derived. This equation implies for both fast input case and slow input case. The critical transition time to for input

$$t_{TO} = \frac{Cc V dd}{2I do} \frac{(n+1)(1-vt)^n}{(1-vt)^{n+1}-(Vv-Vt)^{n+1}}$$

(1)

Where  $Vv = V_{INV/} V_{DD}$  and  $V_{v} = V_{TO/} V_{DD}$ . Then the delay  $t_d$ , the delay from 0.5  $V_{DD}$  of input to 0.5  $V_{DD}$  of output and the effective transition time tout can be expressed as follows tout can be used as for next logic gate.

$(t_{o \leq} t_{TO}; for faster input)$

$$t_{d} = t_{T} \left\{ \frac{1}{2} - \frac{1 - V_{T}}{n+1} + \frac{(V_{v} - V_{t})^{n+1}}{(n+1)(1 - V_{t})^{n}} \right\} + \frac{1}{2} \frac{C_{0}V_{DD}}{ID_{0}}$$

(2)

$$t_{out} = \left\{ \frac{C_0 V_{DD} v_{DO^2}}{0.7 I_{do} (4 V_{DO} - 1)} \right\}$$

(3)

(t<sub>t</sub> for slower input)

$$t_{d} = t_{T} \left[ v_{t} - \frac{1}{2} + \left\{ (v_{v} - v_{T})^{n+1} + \frac{(n+1)(1-V_{T})^{n}}{2t_{T}I_{\frac{DO}{C_{OV_{DD}}}}} \right\}^{\frac{1}{n+1}}$$

(4)

$$t_{out} = \left\{ \frac{c_0 v_{DD}}{0.71 D_0} \left( \frac{1 - V_T}{t_d - \frac{1}{2 - V_T}} \right)^n \right\}$$

(5)

Where n = velocity saturation index, Co is an output capacitance and  $V_{DD} = d_0/V_{DD}$ .

# **3. POWER DISSIPATION IN CMOS INVERTER**

The average power over the interval is

$$p_{avg} = \frac{E}{T} = \frac{1}{T} \int_0^T i_{DD}(t) V_{DD} dt$$

(6)

Where E is the energy consumed over some time interval T is the integral of instaneous power

$$\mathbf{E} = \int_0^T \mathbf{i}_{\text{DD}} \left( \mathbf{t} \right) \mathbf{V}_{\text{DD}} \mathbf{dt}$$

(7)

$P\left(t\right)$  is the instantaneous power drawn from power supply is proportional to supply current i(t) is supply voltage  $V_{DD}$

$$P(t) = i(t)V_{DD}$$

(8)

In CMOS inverter circuit, three types of power dissipation occur.

#### A. Leakage power dissipation

When static current flows from  $V_{DD}$  to ground node, without degrading inputs are called leakage power and the main components of leakage power in the OFF state at band to band tunneling, sub-threshold leakage (I<sub>sub</sub>), gate induced drain leakage, gate tunneling leakage.

#### **B.** Short circuit power

From  $\alpha$ -power law [6], the short circuit power dissipation model is

$$P_{\text{sht.ckt.power}} = V_{\text{DD}} t_{\text{T}} I_{\text{DO}} \frac{1}{\alpha + 1} \frac{1}{2^{\alpha - 1}} \frac{(1 - 2V_{\text{t}})}{(1 - V_{\text{T}})^{\alpha}}$$

(9)

Where  $V_T = V_{TH/}V_{DD}$

## C. Dynamic power dissipation

$D_{\text{ynamic}} = \alpha c_L V_{\text{DD}}^2$  f Where  $\alpha$  is switching activity factor of gate.

# 4. SIMULATION RESULT AND DISCUSSION

Simulation is performed in Cadence tool using Virtuoso analog design environment (ADE), for 45nm technology. This paper emphasize on delay, leakage power and average of CMOS inverter for 45nm technology. Simulation results are obtained from technology by taking input signal pulse having rise time  $(t_r) = \ln s$ , initial delay  $(t_d) = 0ns$ , pulse width= 10ns, time period= 20ns, wp = win = 2wn with this consideration, we compare our result by varying supply voltage for 45nm CMOS inverter thus it can be observed that the delay time decreases with increase in width of PMOS in 45nm technology. The table drawn below, shows how the average power, delay and leakage power changes, with the variation in supply voltages, in both 45nm technology CMOS inverter.

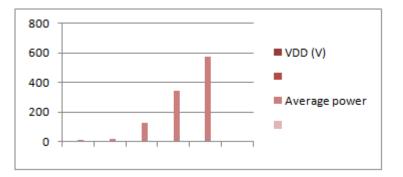

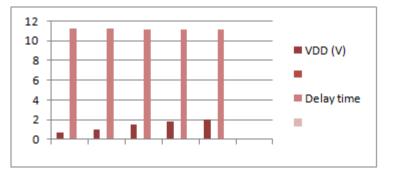

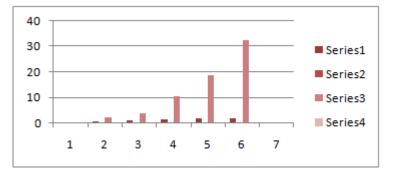

From, the table 1 it can be observed that the delay time decreases with the increase in supply voltage and as the delay decreases. In case of average power and leakage power as the supply voltage increases, then the average power and leakage power increases. As the technology shrinks, the leakage power increases and average power decreases

Figure 2: Average power with the variation of supply voltage

Figure 3: Delay time with the variation of supply voltage

Figure 4: Leakage power with variation of supply voltage

The table drawn below, shows how the average power, delay and leakage power changes, with the variation in supply voltages, in 45nm technology CMOS inverter.

| VDD | Average power            | Delay Time           | Leakage Power            |

|-----|--------------------------|----------------------|--------------------------|

| (V) | (P <sub>avg</sub> in nw) | (t <sub>in ns)</sub> | (P <sub>IKg</sub> in pw) |

| 0.7 | 10.55                    | 11.28                | 2.31                     |

| 1   | 23.06                    | 11.20                | 3.92                     |

| 1.5 | 126.4                    | 11.18                | 10.58                    |

| 1.8 | 345.0                    | 11.17                | 18.69                    |

| 2   | 573.9                    | 11.15                | 32.50                    |

Table 1: Average power, Leakage power and Delay time relate with supply voltage.

## **5.** CONCLUSION

This paper includes UDSM technology in terms of delay, leakage power and average power using CMOS inverter and analyzes how load capacitance, width of transistor and supply voltage effect on average power and delay in 45nm technology. It has been noticed from simulation result that, in 45nm technology, the average power and delay reduces. So, it has been observed that when the channel length less than or equal to 10nm then output waveform are not appeared because the channel length in this range size is below atomic width, which puts the limitation in nano range.

#### ACKNOWLEDGMENT

This work is supported by ITM University Gwalior in collaboration with Cadence Design System, Bangalore India.

### REFERENCES

- [1] Sreenivasa Rao Iii ada, B Ramparamesh, Dr. V.Malleswara Rao, (2011) "Reduction of power dissipation in Logic Circuits", International Journal of Computer Application, Vol. 24, No.6

- [2] SDutta, Shivaling S.Shetti, and Stephen L.Lusky, (1995) "A Comprehensive Delay Model for CMOS Inverters", IEEE Journal of solid-state circuits, Vol. 30, No.8

- [3] Jagannath samanta, Bisunu Prasad De, Banibrata Bag, Raj Kumar Maity, (2012) "Comparative study for delay & power dissipation of CMOS Inverter in UDSM range", International Journal of soft Computing and Engineering (IJSCE),223 1-2307, Vol -I, Issue-6

- [4] T.Sakurai and R.Newton, (1990) "Simple short-channel MOSFET model and its application to delay analysis of Inverter and series-connected MOSFET's." Proceedings of IEEE International conference on Circuits and System, pp. 105-108

- [5] Neil H.E.WESTE, David Harris, Aryan Binaries, (2005) "CMOS VLSI Design: A circuits and System perspective", third edition

- [6] AGhosh, D.Ghosh, (2009), "Optimization of Static Power, Leakage power and Delay of Full Adder Circuit Using Dual Threshold MOSFET Base Design and T-spice simulation", IEEE Computer society, Advances in Recent Technologies in Communication and Computing, PP-903 905

- [7] L.Bisdounis, S.Nikolaidis and O.Koufopavlou, (1995) "Analytical transient response and propogation delay evalution of the CMOS for short - channel devices", IEEE Journal of Solid State Circuits, VoI.33,pp. 302-306

- [8] Samantha, J.,De, B.P., (2012) "Comprehensive analysis of delay in UDSM CMOS circuits, Electrical, Electronics and Computer Science IEEE students conference

- [9] Singh, A.K, Samanta, J, (2012) "Different physical effects in UDSM MOSFET for delay & power estimation: A review, Electrical, Electronics and Computer Science IEEE students, conference

- [10] Li-pen Yuan, Chin-chi Tengt, and Sung-Mo Kang, (1996) "Statistical Estimation of Average Power Dissipation in CMOS VLSI circuits Using Nonparametric Techniques", ISLPED

- [11] T.sakurai, A.R.Newton, (1991) "Delay analysis of series connected MOSFET circuits", IEEE J.Solids-State circuits, vo1.26, pp. 122-13 1

- [12] Pavan, T.K. Naidu, KJ, Babu, M.S, (2011) "Implementation of delay and power monitoring schemes to reduce the power consumption" signals processing, Communication, Computing and Networking Technologies", International conference.

- [13] Tajalli, A Alioto, M., Lebleici, Y., (2009) "Improving Power-Delay Performance of Ultra-low subthreshold SCL circuits", Circuits and system II: Eprsss Briefs, IEEE transaction

- [I4] Govindarajulu, S. Prasad, TJ, "Consideration of performance factors in CMOS design," Electronic Design, 200S.ICED, International Conference.

#### AUTHORS

Shikha Goswami was born on 17th August 1990. She received her B.tech degree in Electronics and Communication Engineering from Shri Rawatpura Institude of Technology and Science Datia (M.P.) India in 2012. She is currently pursuing M.Tech in VLSI Design from Institude of Technology and Management, Gwalior, Madhya Pradesh, India. Her current research interests include VLSI Design, A high speed leakage-Tolerant CMOS Comparator.

Dr. Shyam Akashe was born on 22nd May 1976. This author received his M.Tech from ITM, Gwalior, Madhya Pradesh, India in the year 2006. The author is received Ph.D from Thapar University, Patiala, Punjab in the year 2013. The title of Ph.D thesis topic is Low Power Memory Cell Design. The author's major fields of study are low power VLSI Design, VLSI signal processing, FPGA Design and Communication System. He is working as Associate Professor in Electronics and Communication Engineering department of ITM University, Gwalior, MP, India. He has published about 150 refereed journal and Conference papers. His important research publications are

"Implementation of Technology Scaling on Leakage Reduction Techniques using cadence tools with 45 nm technology," IEEE, 2011; "High Density and Low Leakage Current Based 5T SRAM Cell Using 45 nrn Technology," IEEE, 2011; "Multi Vt 7T SRAM Cell for high speed application At 45 Nm Technology," IEEE, 2011.