# FEASIBLE METHODOLOGY FOR OPTIMIZATION OF A NOVEL REVERSIBLE BINARY COMPRESSOR

Neeraj Kumar Misra, Mukesh Kumar Kushwaha, Subodh Wairya and Amit Kumar

Department of Electronics Engineering, Institute of Engineering and Technology, Lucknow, India

#### **ABSTRACT**

Now a day's reversible logic is an attractive research area due to its low power consumption in the area of VLSI circuit design. The reversible logic gate is utilized to optimize power consumption by a feature of retrieving input logic from an output logic because of bijective mapping between input and output. In this manuscript, we design 4:2 and 5:2 reversible compressor circuits using a new type of reversible gate. In addition, we propose new gate, named as inventive0 gate for optimizing a compressor circuit. The utility of the inventive0 gate is that it can be used as full adder and full subtraction with low value of garbage outputs and quantum cost. An algorithm is shown for designing a compressor structure. The comparative study shows that the proposed compressor structure outperforms the existing ones in terms of garbage outputs, number of gates and quantum cost. The compressor can reduce the effect of carry (Produce from full adder) of the arithmetic frame design. In addition, we implement a basic reversible gate of MOS transistor with less number of MOS transistor count.

#### **KEYWORDS**

Reversible logic, Garbage Output, Quantum cost, Binary Compressor, Low Power VLSI circuit.

#### 1. Introduction

In recent days a reversible design is becoming more popular due to its low power consumption. According to R.Landauer [1], the amount of heat dissipated for every bit of computation information, regardless of its synthesis is KT ln2, where k is the Boltzmann's constant (1.380x10<sup>-23</sup>) and T is the absolute temperature. C.H. Bennett [2] proves that the heat loss in a circuit can be omitted by designing reversible structure by utilizing reversible gates and without feedback and fan-out concept. Reversible design is based on two concepts: logic reversibility means input and output must be uniquely retrievable from each other and second concept that logic work in backward and in each operation no heat dissipation and satisfies physical reversibility [5, 13, 15]. Therefore, they potentially help to solve at least two problems: overheating and power saving [7, 8, 10, 16]. The reversible logic may be especially important in low power VLSI application.

The compressor has wide application in reducing power during the frame of the partial product design and the different types of addition operations design [4, 14, 15, 21, 22]. The compressor reduces the critical path, architectural complexity and the impact of carry generated from full adder operations. The manuscript is organised with the following sections: Section 2 gives the basic definition of reversible logic and its inverse property. Section 3 shows the basic reversible gate in MOS transistor realization. Section 4 introduces new reversible compressor structure like 4:2 and 5:2 compressor circuits with it discuss parameter. Section 5 gives the comparative analysis table with its existing design. Finally, the manuscript is concluded and references.

DOI: 10.5121/vlsic.2015.6401

# 2. BASIC DEFINITIONS RELATED TO REVERSIBLE LOGIC

In this section, we show the fundamentals of reversible logic, which are relevant to this manuscript.

**Definition 2.1:** A Reversible gate (denoted by n x n) is an n-input, n- output circuit which generates a unique output vector from each possible input vector [11, 12].

**Definition 2.2 :** A logic gate L is reversible if, for any output y, there is a unique input x such that, L(x)=y

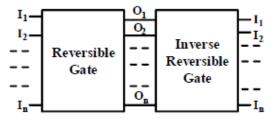

If a gate L is reversible, there is an inverse gate L' which maps y to x for which L'(y)=x. It is an n-input n-output logic function in which there is a one-to-one correspondence between the inputs and the outputs means in no information loss. Because of this bijective mapping the input and output vector and can be uniquely determined from the output vector. This prevents the loss of information which is the root cause of power dissipation in irreversible logic circuits [6, 9, 12]. Cascading of reversible and inverse reversible gate is shown in Figure 1.

Figure 1. Cascading of reversible and inverse reversible gate.

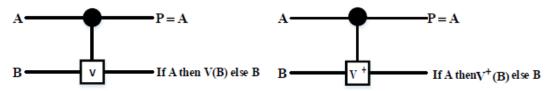

**Definition 2.3 :** Quantum cost is one important metric, which is the number of 2x2 XOR, controlled-V or controlled-V<sup>+</sup> constitute the quantum cost of the structure. Figs 2a, b depicts the controlled-V and Controlled-V<sup>+</sup> gate [17, 19].

Figure 2. Quantum realization of controlled (V and V<sup>+</sup> gate)

Table 1a. Functionality table of some reversible gates.

| Reversible gates | Operation<br>Realization | Quantum<br>cost | Quantum circuit                                        |  |

|------------------|--------------------------|-----------------|--------------------------------------------------------|--|

| TG               | NOT, OR, AND             | 5               | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

| PG               | NOT, OR, AND, XOR        | 4               | A — A A A A A A A A A A A A A A A A A A                |  |

# 3. RELATED WORKS

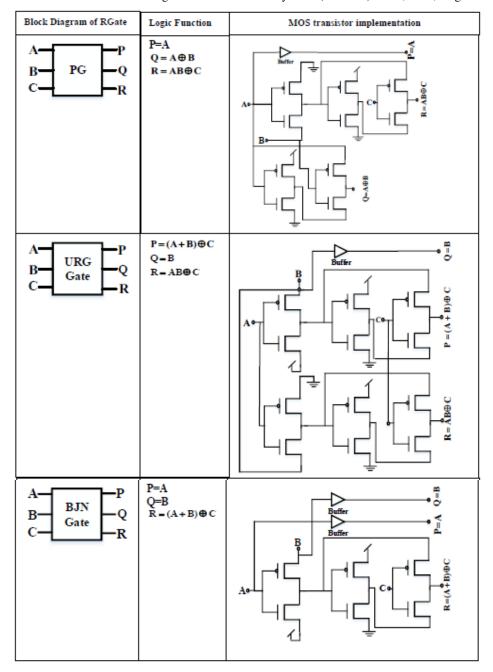

In this section, we implemented basic reversible gates like CNOT, TG, F2G, PG, FRG, BJN and URG in MOS transistor by using Gate diffusion input (GDI) technique. This technique reduces the power, delay and area [20] because the reversible logic circuit design that conserve information by one-to-one mapping between input and output logic.

Block Diagram of RGate Logic Function MOS transistor implementation P=A  $Q = A \oplus B$ FG Q=B R = AB⊕C TG B٠ •Q≖B P=A Q=A + B F2G -Q  $R = A \oplus C$ В P=A •P=A Q = AB + AC FRG  $R = AB + \overline{AC}$

Table 1b. Reversible 2x2 type gates.

# 4. PROPOSED COMPRESSOR DESIGN

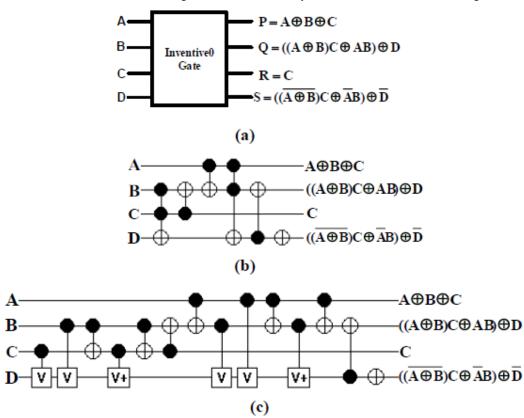

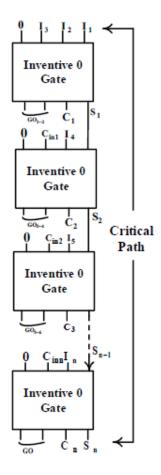

In this section, we design a compact reversible compressor. A compressor reduces the impact of carry (Originated from full adder) of arithmetic frame operations. To construct a compressor we using inventive0 gate for optimizing the compressor circuit. Inventive0 gate is 4x4 type reversible gate (Figure 3). The corresponding truth table (Table 3) of inventive0 gate verified that bijective mapping exist between input and output. The hardware complexity and quantum cost of inventive0 gate are  $7\alpha+4\beta+3\delta$  and 10 respectively.

International Journal of VLSI design & Communication Systems (VLSICS) Vol.6, No.4, August 2015

Figure 3. Reversible 4x4 Inventive0 gate. (a) Block diagram. (b) Toffoli gate representation of Inventive0 gate. (c) Quantum implementation of Inventive0 gate using primitive gates.

# 4.1 Some Utility of New Type of Gate

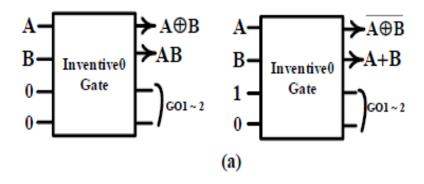

The proposed new gate, a universal gate in the sense it implements all Boolean functions. When set C=D=0, the inventive0 gate simultaneously realised the XOR logic function and the AND logic function as drawn in Fig 4a. Similarly, set C=1 and D=0 the inventive0 gate realised the XNOR logic function and OR logic function as drawn in Fig 4b. The inventive0 gate also work as a reversible full adder and full subtraction logic function, as drawn in Fig. 4c.

Figure 4. (a) Inventive0 gate utilized as XOR and AND gates. (b) Inventive0 gate utilized as XNOR and OR gates. (c) Inventive0 gate utilized as full adder and full subtraction

| Inputs |   |   |   | Outputs |   |   |   |

|--------|---|---|---|---------|---|---|---|

| A      | В | C | D | P       | Q | R | S |

| 0      | 0 | 0 | 0 | 0       | 0 | 0 | 1 |

| 0      | 0 | 0 | 1 | 0       | 1 | 0 | 0 |

| 0      | 0 | 1 | 0 | 1       | 0 | 1 | 0 |

| 0      | 0 | 1 | 1 | 1       | 1 | 1 | 1 |

| 0      | 1 | 0 | 0 | 1       | 0 | 0 | 0 |

| 0      | 1 | 0 | 1 | 1       | 1 | 0 | 1 |

| 0      | 1 | 1 | 0 | 0       | 1 | 1 | 0 |

| 0      | 1 | 1 | 1 | 0       | 0 | 1 | 1 |

| 1      | 0 | 0 | 0 | 1       | 0 | 0 | 1 |

| 1      | 0 | 0 | 1 | 1       | 1 | 0 | 0 |

| 1      | 0 | 1 | 0 | 0       | 1 | 1 | 1 |

| 1      | 0 | 1 | 1 | 0       | 0 | 1 | 0 |

| 1      | 1 | 0 | 0 | 0       | 1 | 0 | 1 |

| 1      | 1 | 0 | 1 | 0       | 0 | 0 | 0 |

| 1      | 1 | 1 | 0 | 1       | 1 | 1 | 0 |

| 1      | 1 | 1 | 1 | 1       | 0 | 1 | 1 |

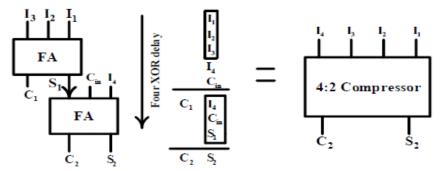

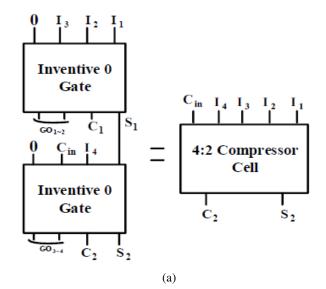

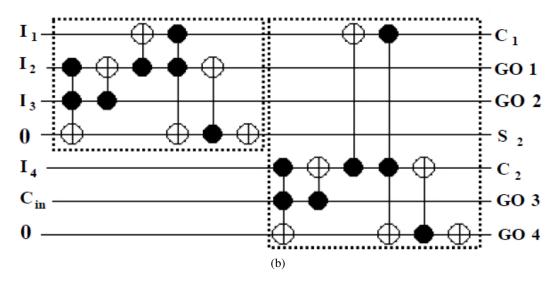

# **4.2 Proposed reversible 4:2 Compressor circuit**

In this subsection, we design a 4:2 compressor circuit using inventiv0 gate. This compressor circuit contains 2 gates (2 x inventive0), it requires four inputs (I1, I2, I3, I4) and two outputs (C2, S2) along with a carry-in (Cin) and a carry-out (C1) and two constant inputs. The proposed compressor block diagram and quantum realization as depicted in Figs 6a, b. The quantum cost of this 4:2 compressor circuit is 20, because the QC (4:2 compressor) = 2x QC (Inventive0 gate) = 2x10=20.

Total logical calculation (T) of the compressor circuit is

$$T_{inventive0} = (3\alpha)$$

(for Q expression) +  $(2\alpha+2\beta)$  (for R expression) +  $(2\alpha+2\beta+3\delta)$  (for S expression) =  $7\alpha+4\beta+3\delta$

T (Design 4:2 compressor) =  $2x T_{inventiv0} = 2x (7\alpha + 4\beta + 3\delta) = 14\alpha + 8\beta + 6\delta$

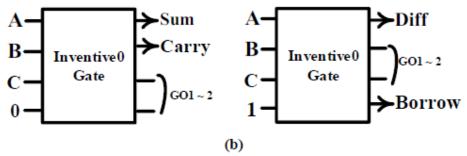

Figure 5. Conventional compressor structure.

Figure 6. Proposed design of 4:2 reversible compressor.

(a) Block diagram representation.

(b) The proposed Quantum realization.

#### Algorithm I: Construction of reversible 4:2 compressor.

#### 1. Begin

```

Pick up first Inventive0 gate and pick input I<sub>1</sub>, I<sub>2</sub> and I<sub>3</sub>, Inputs and outputs block are considered to be levels I and O.

```

```

2. I[I_1] = C[O_1] = I_1,

I[I_2]=C[O_2]=I_2

// Input of 1st Inventive0 gate.

I[I_3]=C[O_3]=I_3;

// Output of 1st Inventive0 gate.

3. O[O_1]=C[O_1] \oplus C[O_2] \oplus C[O_3],

O[O_2]=((C[O_1] \oplus C[O_2]) C[O_3])+(C[O_1] C[O_2]) \oplus 0),

O[O_3] = C[O_3] = I_3,

O[O_4] = (((C[O_1] \oplus C[O_2]) \oplus 1)C[O_3] + ((C[O_1] \oplus 1) C[O_2]) \oplus 1),

4. Pick up second Inventive0 gate and pick input S1, I4 and Cin, level P

5. P[I_1] = P[O_1] = S_1,

P[I_2]=P[O_2]=I_4,

// Input of 2<sup>nd</sup> Inventive0 gate.

P[I_3]=P[O_3]=C_{in};

// Output of 2<sup>nd</sup> Inventive0 gate.

P[O<sub>1</sub>]=P[O<sub>1</sub>] ⊕ P[O<sub>2</sub>] ⊕ P[O<sub>3</sub>],

P[O_2]=((P[O_1] \oplus P[O_2])P[O_3]+(P[O_1]P[O_2]) \oplus 0),

P[O_3] = P[O_3] = C_{in}

P[O_4] = (((P[O_1] \oplus P[O_2]) \oplus 1)P[O_3]) + \{(P[O_1] \oplus 1) P[O_2]\} \oplus 1)

End

```

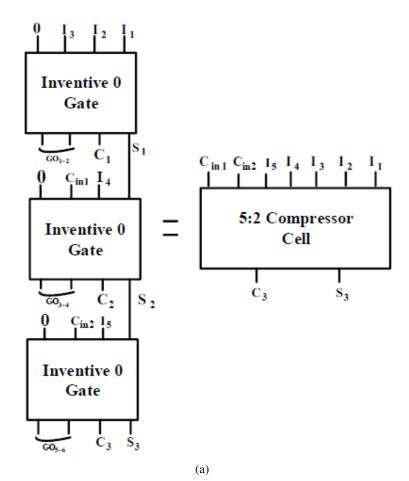

# 4.3. Proposed reversible 5:2 Compressor circuit

In this subsection, we design a 5:2 compressor circuit. This design has five primary inputs  $(I_1, I_2, I_3, I_4, I_5)$  and two primary outputs (C2, S2) along with two carry-in (Cin1, Cin2) and three constant inputs. The block diagram of 5:2 compressor and quantum realization as depicted in Figs 7a, b.

The quantum cost of this 5:2 compressor is 30, because the QC (5:2 compressor) = 3x QC (InventiveOgate) = 3x10=30.

T (Design 5:2 compressor) = 3 Tinventiv0=  $3x (7\alpha+4\beta+3\delta) = 21\alpha+12\beta+9\delta$

Total logic calculation (Circuit cost): One of the important parameter of circuit is its architectural complexity.

Where  $\alpha$ = Count of two input XOR gate.

$\beta$ =Count of two input AND gate.

And  $\delta$ = Count of NOT gate.

T=Total logical calculation.

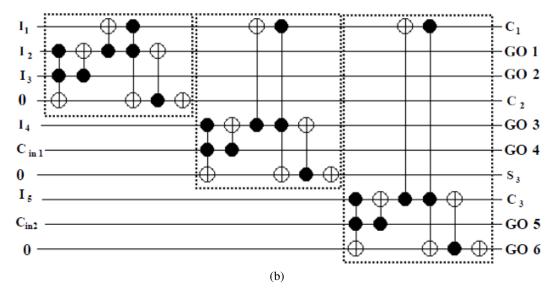

# Algorithm II: Construction of reversible n: 2 compressor.

#### Begin

Here n is the reversible compressor circuit input.

- If n > 4 then

- 2. Utilise one inventive0 gate as initial compressor gives the outputs of a n:2 reversible compressor.

# Loop Step 3 for

- 3. Cascade another (n-3) inventive0 gate by using input of initial compressor and addition inputs

- 4. End loop

- 5. Else Use initial inventive0 gate compressor

- 6. End if

- 7. End

Figure 7. Proposed design of 5:2 reversible compressor.

- (a) Block diagram representation.

- (b) The proposed Quantum realization

Figure 8. Design of n:2 reversible compressor

International Journal of VLSI design & Communication Systems (VLSICS) Vol.6, No.4, August 2015

**Lemma 1:** A reversible n:2 compressor can be realised with (n-2) gates, where n is the input of compressor.

**Proof:** A 4:2 compressor consist of two inventive0 gate. Hence the total number of gates required to construct the 4:2 compressor is

NOG (4:2 compressor) = NOG (2x inventive0 gate) = 2 = 1 + (4-3) = 1 + (n-3)

Hence the statement holds for the base case n = 4

Assume that, the statement true for n = m, Hence, a reversible m:2 compressor requires at least (m-2) reversible gates.

**Lemma 2:** A reversible n:2 compressor can be realised with 10(n-3) quantum cost, where n is the input of compressor.

**Proof:** A 4:2 compressor circuit is constructed with one inventive0 gate. Hence the total quantum cost of the 4:2 compressor circuit is

QC (4:2 compressor) = QC (2x inventive0 gate) = 10 = 10 (4 - 3)

Hence the statement hold for the base case n = 4

Assume that, the statement true for n=m, Hence a reversible m:2 compressor can be realized with 10(m-3) quantum cost.

**Lemma 3:** A reversible n:2 compressor generates at least (2n-4) garbage outputs, where n is the input of compressor.

**Proof:** A 4:2 compressor circuit contains one inventive0 gate. Hence the total garbage outputs produce by 4:2 compressor is at least

$GO(4:2 \text{ compressor}) = GO(2x \text{ inventive 0 gate}) = 4 = (4 \times 2 - 4)$

Hence, the statement holds for the base case n=4

Assume that, the statement true for n=m. Hence, a reversible m:2 compressor produce at least (2n-4) garbage outputs.

**Lemma 4:** A reversible n:2 compressor can be realised with (n-2) ancilla input, where n is the input of compressor.

**Proof:** A 4:2 compressor consist of two inventive0 gate. Hence the total ancilla input required to construct the 4:2 compressor is

CI (4:2 compressor) = CI (2x inventive0 gate) = 2 = 1 + (4-3) = 1 + (n-3)

Hence the statement holds for the base case n = 4

Assume that, the statement true for n = m, Hence, a reversible m:2 compressor requires at least (m-2) ancilla input.

### 5. PERFORMANCE EVALUATION ANALYSIS

In this section, we have shown performance evaluation analysis with the help of figures and comparative tables. We implement basic reversible gate in MOS transistor count it is depicted in Figure 8. Table 4 shows that the performance of our 4:2 compressor circuit is better compared to existing designs.

Figure 9. Number of MOS transistor count in different reversible gate

Table 4. Comparative analysis table of 4:2 compressor

| 4:2 Compressor<br>Structures | Gate count | Constant inputs | Garbage outputs | Quantum cost |

|------------------------------|------------|-----------------|-----------------|--------------|

| Proposed                     | 2          | 2               | 4               | 20           |

| Existing design 1 [3]        | 4          | 3               | 5               | 28           |

| Existing design 2 [3]        | 7          | 3               | 5               | 20           |

| Existing design 4 [3]        | 2          | 2               | 3               | 26           |

| Existing design 4 2 [15]     |            | 3               | 5               | 18           |

#### 6. CONCLUSIONS

In this manuscript there are two main parts; the first part deals with implementing basic reversible gates CNOT, FG, TG, PG, BJN and URG gate in MOS transistor using Gate diffusion input (GDI) technique. The MOS transistor for basic reversible gate are designed by keeping in mind for the minimum MOS transistor count and also reducing the critical path. In addition, it shows a comparative performance table to the realization of the MOS transistor count. However, in the second part, we propose 4:2 compressor and 5:2 compressor circuits using inventive0 gate and also its quantum circuits. These designs are the most effective among all other existing design in terms of gate count, garbage outputs and quantum cost. Since compressor can be used in low power VLSI circuit for reducing the impact of carry (Generated from full adder operation) of arithmetic frame design, This compressor structure will be definitely used in low power circuit, ALU, quantum computers etc.

#### REFERENCES

- [1] R.Landauer, (1961) "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, pp.183-191.

- [2] C H Bennett, (1973) "Logical Reversibility of Computation," IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532.

- [3] Soghra shoaei, Majid Haghparast, (2014) "Novel designs of nanometric parity preserving reversible compressor", Quantum information process, vol 13,issue 8, pp. 1701-1714.

- [4] Majid Haghparast, Majid Mohammadi, (2010) "Novel quantum compressor designs using new genetic algorithm based simulator, analyzer and synthesizer software in nanotechnology". International Journal of Quantum Information. 8, pp. 1219–1231.

- [5] Neeraj Kumar Misra, Subodh Wairya, Vinod Kumar Singh, (2014) "An Inventive Design of 4\*4 Bit Reversible NS Gate" IEEE International Conference on Recent Advances and Innovation in Engineering (ICRAIE-2014), pp. 1219-12316

- [6] Sajib Kumar Mitra and Ahsan Raja Chowdhury, (2012) "Minimum cost fault tolerant adder circuits in reversible logic synthesis", 25th Int. Conf. VLSI Design, VLSID, pp. 334-339.

- [7] Hafiz Md. Hasan Babu, Nazir Saleheen, Lafifa Jamal, Sheikh Muhammad Sarwar, Tsutomu Sasao (2014) "Approach to design a compact reversible low power binary comparator" IET Computers & Digital Techniques" Vol. 8, Iss. 3, pp. 129–139.

- [8] Neeraj Kumar Misra, Subodh Wairya and Vinod Kumar Singh, (2015) "Approaches to Design Feasible Error Control Scheme Based on Reversible Series Gates", European Journal of Scientific Research vol. 129, No. 3, pp. 224-240.

- [9] Neeraj Kumar Misra, Mukesh Kumar Kushwaha, Subodh Wairya and Amit Kumar, (2015) "Cost Efficient Design of Reversible Adder Circuits for Low Power Applications", International Journal of Computer Applications, 117(19), pp. 37-45.

- [10] S. Islam, M. M. Rahman, Z. Begum and M. Z. Hafiz, (2010) "Realization of a novel fault tolerant reversible full adder circuit in nanotechnology", The International. Arab J. Inform. Technol.7, pp. 317–322.

- [11] Neeraj Kumar Misra, Subodh Wairya and Vinod Kumar Singh, (2014) "EVOLUTION OF STRUCTURE OF SOME BINARY GROUP-BASED NBit COMPARATOR, NTo-2 N DECODER BY REVERSIBLE TECHNIQUE, N-TO-2N DECODER BY REVERSIBLE TECHNIQUE" International Journal of VLSI design & Communication Systems (VLSICS), Vol.5,No. 5: pp. 9-22

- [12] Majid Haghparast and Keivan Navi, (2008) "A novel fault tolerant reversible gate for nanotechnology based systems', American Journal of Applied Sciences. 5, pp. 519–523.

- [13] Neeraj Kumar Misra, Subodh Wairya, Vinod Kumar Singh, (2014) "Preternatural Low-Power Reversible Decoder Design in 90 nm Technology Node" International Journal of Scientific & Engineering Research, Volume 5, Issue 6, pp. 969-978.

- [14] J. W. Bruce, M. A. Thornton, L. Shivakumaraiah, P. S. Kokate, and X. Li, (2002) "Efficient adder circuits based on a conservative reversible logic gate," in Proceedings of IEEE Symposium on VLSI, pp. 83–88.

- [15] Majid Haghparast, Soghra Shoaci, (2015) "Design of a New Parity Preserving Reversible Full adder", Journal of Circuits Systems and Computers, world scientific, vol 24, no. 1, pp: 1550006-11.

- [16] SubodhWairya, Rajendra Kumar Nagaria, Sudarshan Tiwari, (2012) "Performance Analysis of High Speed Hybrid CMOS Full Adder Circuits for Low Voltage VLSI Design", Hindawi Publishing Corporation VLSI Design.

- [17] Bibhash Sen, AyushRajoria and BiplabK.Sikdar, (2013) "Design of Efficient Full adder in Quantum-Dot cellular Automata" The scientific World Journal Hindawi Publishing Corporation, pp. 1-10

- [18] Pallavi devi gopineedi, Himanshu Thapliyal, M.B Srinivas and Hamid R. Arabnia,(2006) "Novel and Efficient 4:2 and 5:2 compressor with minimum number of transistor designed for low power operation" In ESA, pp. 160-168.

- [19] Bibhash Sen, Siddhant Ganeriwal and Biplab K. Sikdar, (2013) "Reversible Logic-Based Fault-Tolerant Nanocircuits in QCA", ISRN Electronics Hindawi Publishing Corporation.

- [20] Adarsh Kumar Agrawal, S.Wairya, R.K. Nagaria and S.Tiwari, (2009) "A New Mixed Gate Diffusio Input Adder Topology for High Speed Low Power Digital Circuits", World Applied Sciences Journal, pp. 138-144.

- [21] Neeraj Mishra, and Asmita Haveliya, (2013) "An advancement in the Nx N Multiplier Architecture Realization via the Ancient Indian Vedic Mathematics." IJECCE 4, no. 2 pp. 544-548.

- [22] Chip-Hong Chang, Jiangmin Gu, and Mingyan Zhang, (2004), "Ultra low-voltage low-power CMOS 4-2 and 5-2 compressors for fast arithmetic circuits." Circuits and Systems I: Regular Papers, IEEE Transactions on 51, no. 10, pp: 1985-1997.